### UNIVERSITÀ DEGLI STUDI DI PARMA

DOTTORATO DI RICERCA IN "TECNOLOGIE DELL'INFORMAZIONE"

CICLO XXXIII

# Advanced FPGA-Based Systems Design Techniques for Wearable Sensor Applications

Coordinatore: Chiar.mo Prof. Marco Locatelli

Relatore: Chiar.ma Prof.ssa Ilaria De Munari Tutor: Chiar.ma Prof.ssa Valentina Bianchi

Dottorando: Marco Bassoli

Anni Accademici 2017/2018 - 2019/2020

Dedicated to My Family

# Contents

|   | Intr              | oductio | n                                 | 1               |  |  |  |  |  |

|---|-------------------|---------|-----------------------------------|-----------------|--|--|--|--|--|

| 1 | Background        |         |                                   |                 |  |  |  |  |  |

|   | 1.1               | Suppor  | rt Vector Machine Algorithms      | 5               |  |  |  |  |  |

|   |                   | 1.1.1   | Kernelized Support Vector Machine | 7               |  |  |  |  |  |

|   |                   | 1.1.2   | Multiclass Problem                | 9               |  |  |  |  |  |

|   | 1.2               | Model   | -Based Design                     | 10              |  |  |  |  |  |

|   | 1.3               | Posit N | Numbers Theory                    | 11              |  |  |  |  |  |

|   |                   | 1.3.1   | Regime Variable Length            | 13              |  |  |  |  |  |

|   |                   | 1.3.2   | Special Cases                     | 13              |  |  |  |  |  |

| 2 | Rela              | nted Wo | orks                              | 15              |  |  |  |  |  |

|   | 2.1               | Smart   | Home Systems                      | 15              |  |  |  |  |  |

|   | 2.2               | State o | of the Art in HAR                 | 18              |  |  |  |  |  |

|   |                   | 2.2.1   | Hardware Solutions                | 20              |  |  |  |  |  |

|   |                   | 2.2.2   | Firmware and Software             | 24              |  |  |  |  |  |

|   |                   | 2.2.3   | Wearable Devices                  | 28              |  |  |  |  |  |

|   |                   |         |                                   |                 |  |  |  |  |  |

| 3 | Env               | ironmeı | ntal Sensors                      | 33              |  |  |  |  |  |

| 3 | <b>Env</b><br>3.1 |         | ntal Sensors Consumption Analysis | <b>33</b><br>37 |  |  |  |  |  |

| Wea | rable S                   | ensor for Human Activity Recognition               | 45  |  |  |  |  |

|-----|---------------------------|----------------------------------------------------|-----|--|--|--|--|

| 4.1 | Wearable Sensor Prototype |                                                    |     |  |  |  |  |

| 4.2 | The H                     | uman Activity Dataset                              | 48  |  |  |  |  |

| 4.3 | Algori                    | ithm                                               | 51  |  |  |  |  |

|     | 4.3.1                     | Training and Inference Computations                | 52  |  |  |  |  |

|     | 4.3.2                     | Core SVM Selection                                 | 52  |  |  |  |  |

|     | 4.3.3                     | Core SVM Analysis                                  | 54  |  |  |  |  |

|     | 4.3.4                     | Features Calculation                               | 55  |  |  |  |  |

| 4.4 | Hardw                     | /are                                               | 56  |  |  |  |  |

|     | 4.4.1                     | Support Vector Machine Modeling                    | 58  |  |  |  |  |

|     | 4.4.2                     | Support Vector Machine Hardware Design             | 63  |  |  |  |  |

|     | 4.4.3                     | FPGA Implementation                                | 68  |  |  |  |  |

| 4.5 | Hardw                     | vare Investigation I: Pipelined Accumulators       | 70  |  |  |  |  |

|     | 4.5.1                     | Model-Based Single-Set DB                          | 75  |  |  |  |  |

|     | 4.5.2                     | Model-Based Multiple-Set DB                        | 82  |  |  |  |  |

|     | 4.5.3                     | Stand-Alone Model-Based Accumulator Implementation | 86  |  |  |  |  |

|     | 4.5.4                     | SVM Kernel Implementation                          | 91  |  |  |  |  |

| 4.6 | Hardw                     | vare Investigation II: Posit Numeric Format        | 98  |  |  |  |  |

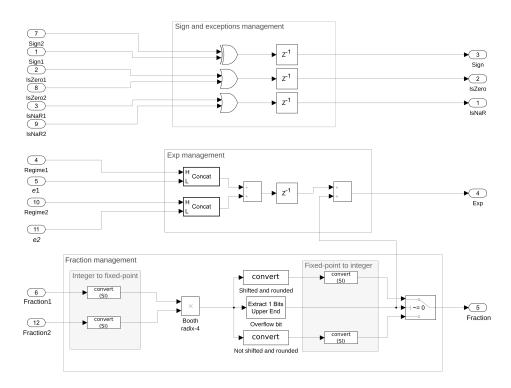

|     | 4.6.1                     | Architecture of a Posit Multiplier                 | 99  |  |  |  |  |

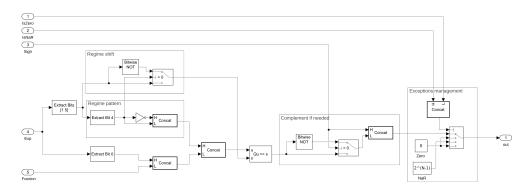

|     | 4.6.2                     | Model-Based Multiplier Implementation              | 100 |  |  |  |  |

|     | 4.6.3                     | Methodology                                        | 110 |  |  |  |  |

|     | 4.6.4                     | Results                                            | 118 |  |  |  |  |

| Con | clusion                   |                                                    | 123 |  |  |  |  |

| Bib | iograpł                   | ıy                                                 | 146 |  |  |  |  |

| Not | es                        |                                                    | 147 |  |  |  |  |

| Ack | nowled                    | gments                                             | 149 |  |  |  |  |

<u>ii</u>\_\_\_\_\_

# **List of Figures**

| 1   | Sensors system for behavioral analysis.                                                                                                     | 2  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1 | Support Vector Machine linear example: (a) input-output function,                                                                           |    |

|     | (b) features space, (c) features space with threshold line                                                                                  | 6  |

| 1.2 | Best fitting threshold line                                                                                                                 | 7  |

| 1.3 | Kernelized Support Vector Machine example: (a) single-feature lin-<br>ear (top) and kernelized (bottom) example, (b) original input feature |    |

|     | space with kernelized threshold, (c) kernelized input feature space.                                                                        | 8  |

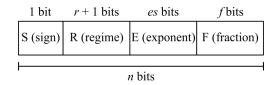

| 1.4 | Bit-field representation of a Posit number.                                                                                                 | 11 |

| 1.4 |                                                                                                                                             | 11 |

| 2.1 | Wi-Fi system architecture.                                                                                                                  | 18 |

| 2.2 | IBM Bluemix Watson dashboard reporting Wi-Fi sensors activity and                                                                           |    |

|     | battery level                                                                                                                               | 19 |

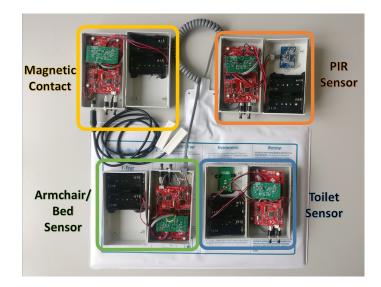

| 3.1 | The sensors prototypes. PIR = Passive InfraRed                                                                                              | 35 |

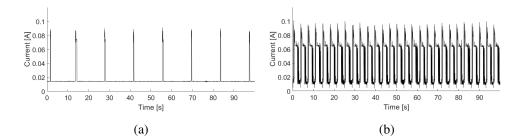

| 3.2 | Current absorption measurements: (a) scenario with missing Wi-Fi                                                                            |    |

|     | network connection; (b) scenario with sensor connected to Wi-Fi but                                                                         |    |

|     | without internet access.                                                                                                                    | 39 |

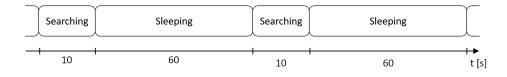

| 3.3 | Working phases for both Wi-Fi and Internet absence scenarios                                                                                | 40 |

| 3.4 | Current absorption measurements of sensors running with the intro-                                                                          |    |

|     | duced sleep periods: (a) scenario with missing Wi-Fi network con-                                                                           |    |

|     | nection; (b) scenario with sensor connected to Wi-Fi but without in-                                                                        |    |

|     | ternet access.                                                                                                                              | 40 |

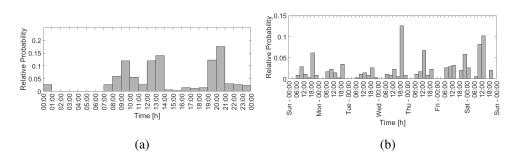

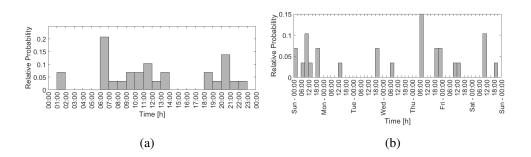

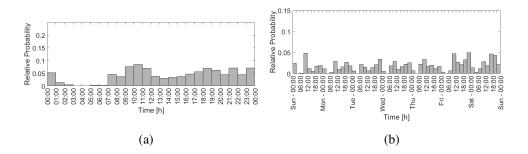

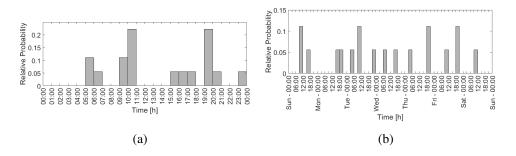

| 3.5  | Armchair sensor activity during the day (a) and during the week (b).         | 43 |

|------|------------------------------------------------------------------------------|----|

| 3.6  | Magnetic contact (door sensor) activity during the day (a) and during        |    |

|      | the week (b).                                                                | 44 |

| 3.7  | PIR sensor activity during the day (a) and during the week (b)               | 44 |

| 3.8  | Toilet sensor activity during the day (a) and during the week (b). $\ .$ .   | 44 |

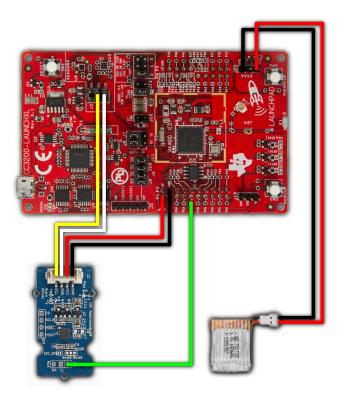

| 4.1  | The WiFi wearable sensor including the LaunchPadXL board and the             |    |

|      | inertial measurement unit (IMU) board.                                       | 46 |

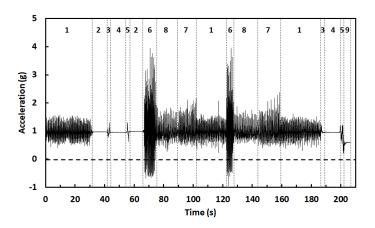

| 4.2  | Example of the accelerometer x-axis reading. The activities performed        |    |

|      | during data acquisition have been highlighted, reporting the corre-          |    |

|      | sponding activity ID.                                                        | 49 |

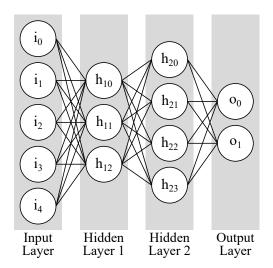

| 4.3  | Example of a neural network with two hidden layers and: five nodes           |    |

|      | at the input layer, three nodes at the first hidden layer, four nodes at     |    |

|      | the second hidden layer, and two nodes at the output layer                   | 51 |

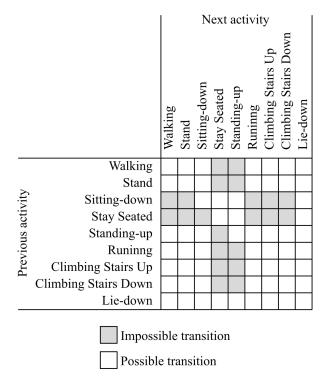

| 4.4  | Matrix identifying the possible/impossible transitions to be used in         |    |

|      | the post-processing algorithm phase.                                         | 54 |

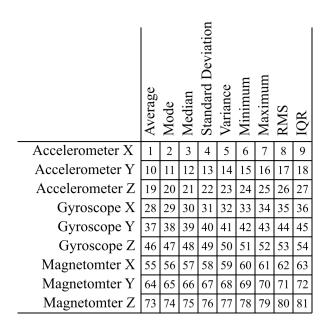

| 4.5  | Representation of the features vector <b>x</b> . The numbers are the indexes |    |

|      | of the elements inside the vector                                            | 57 |

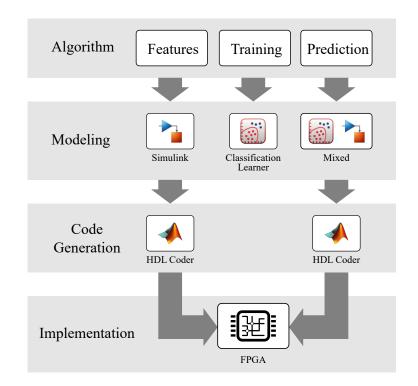

| 4.6  | Model-based development workflow                                             | 59 |

| 4.7  | Full activity recognition algorithm model.                                   | 59 |

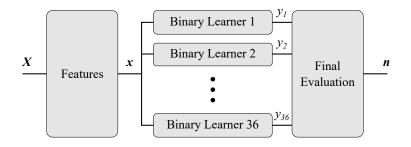

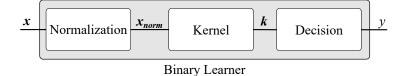

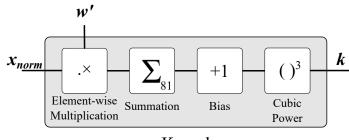

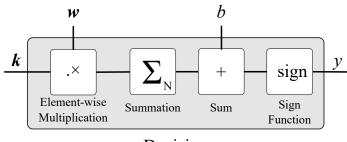

| 4.8  | Single binary learner model.                                                 | 60 |

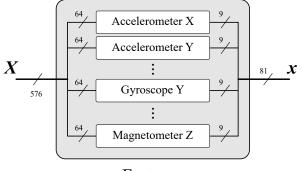

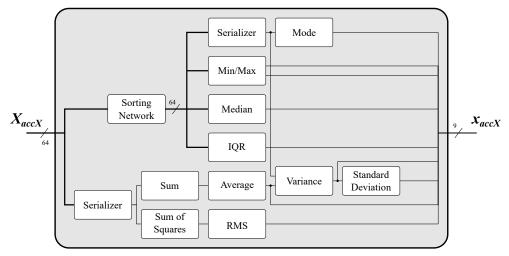

| 4.9  | Overview of the features calculation modeling.                               | 60 |

| 4.10 | Modeling example of features computation for the accelerometer's X           |    |

|      | axis, i.e. one of the 9 input channels                                       | 61 |

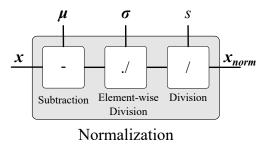

| 4.11 | Modeling of one Binary Learner normalization phase                           | 61 |

| 4.12 | Modeling of one Binary Learner kernel phase                                  | 62 |

| 4.13 | Modeling of one Binary Learner decision phase                                | 62 |

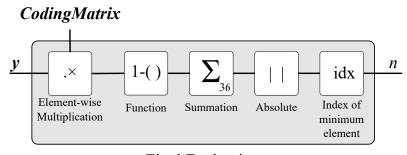

| 4.14 | Modeling of the Final Evaluation phase of the system                         | 63 |

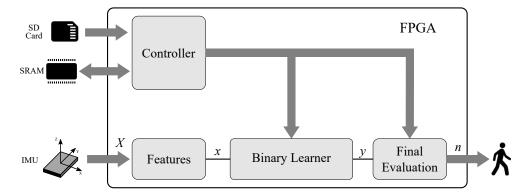

| 4.15 | Architecture of the final system to be implemented in the FPGA               | 64 |

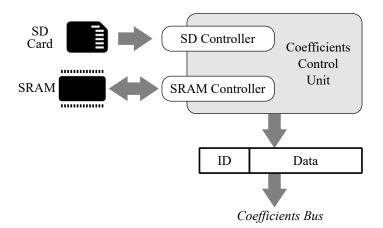

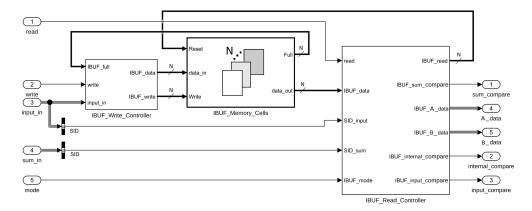

| 4.16 | Memory Controller architecture.                                              | 65 |

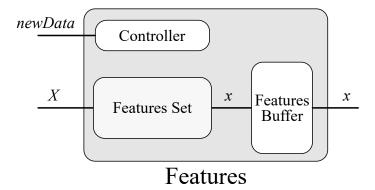

| 4.17 | Features calculation final architecture.                                     | 66 |

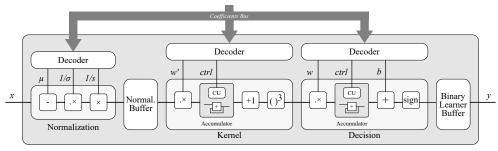

| 4.18 | Binary Learner final architecture.                                                                                                    | 67 |

|------|---------------------------------------------------------------------------------------------------------------------------------------|----|

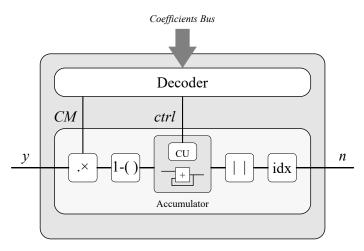

| 4.19 | Final Evaluation architecture. Here, the <i>CodingMatrix</i> is reported ad <i>CM</i>                                                 | 69 |

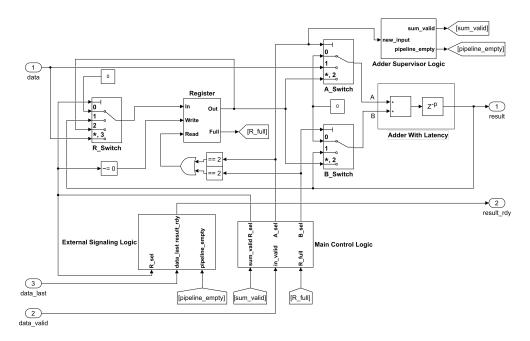

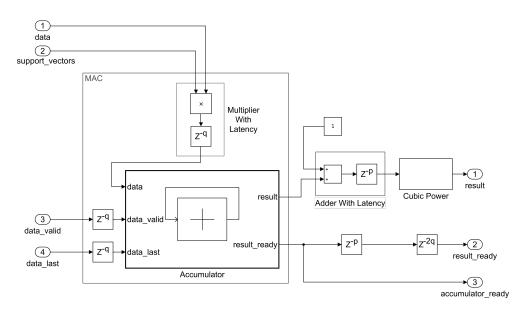

| 4.20 | The Simulink accumulator model based on the work of [119]. In this example, the system has been configured to model a pipelined accu- |    |

|      | mulator with an adder latency of <i>p</i> clock cycles                                                                                | 77 |

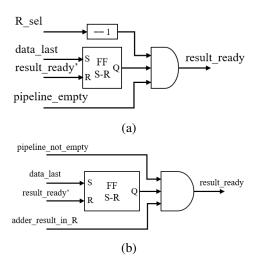

| 4.21 | (a) External Signaling Logic function; (b) Adder Supervisor Logic                                                                     |    |

|      | function                                                                                                                              | 79 |

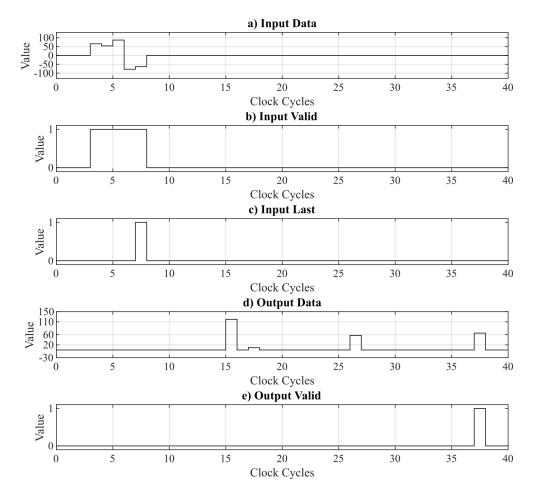

| 4.22 | Example of an execution of the accumulator model: (a) Input data                                                                      |    |

|      | values; (b) External data valid input signal (data_valid); (c) External                                                               |    |

|      | input signal to notify the last value of the set (data_last); (d) Out-                                                                |    |

|      | put value (result); (e) Internally generated output signal to notify the                                                              |    |

|      | output is valid (result_ <i>ready</i> )                                                                                               | 81 |

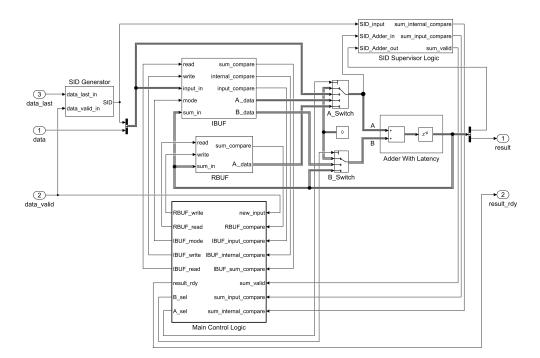

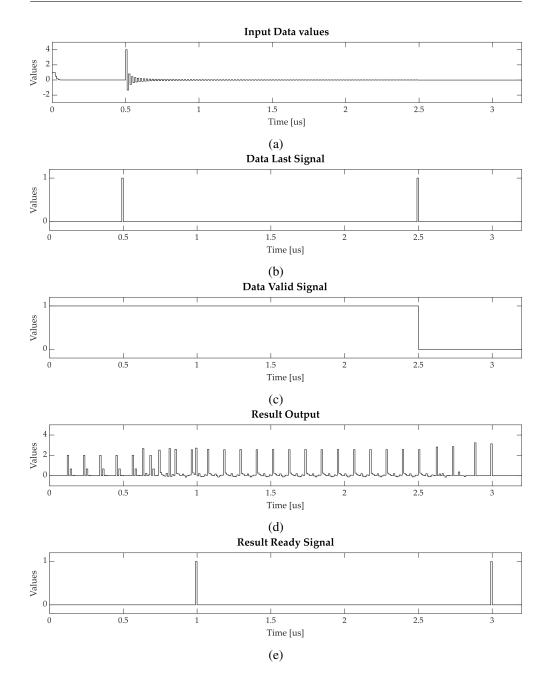

| 4.23 | Simulink multi-set delayed buffering (DB) accumulator implementa-                                                                     |    |

|      | tion                                                                                                                                  | 83 |

| 4.24 | Architecture of the Input Buffer (IBUF) block.                                                                                        | 85 |

| 4.25 | Input and output signals of the multi-set DB accumulator in Simulink                                                                  |    |

|      | simulation: (a) Input vector values, (b) <i>Data_last</i> signal, (c) <i>Data_valid</i>                                               |    |

|      | signal, (d) Accumulator output value, and (e) <i>Result_ready</i> signal                                                              | 87 |

| 4.26 | Simulink cubic kernel implementation                                                                                                  | 92 |

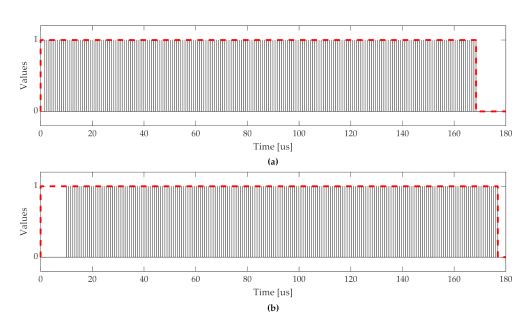

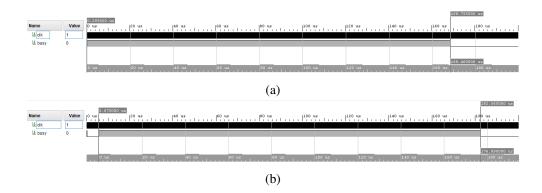

| 4.27 | Kernel performance in Simulink simulations: (a) Kernel with pro-                                                                      |    |

|      | posed accumulator, (b) Kernel with Simulink IP accumulator                                                                            | 94 |

| 4.28 | Xilinx Vivado post-implementation results of the kernel with (a) Ker-                                                                 |    |

|      | nel with proposed accumulator, (b) Kernel with Simulink IP accumu-                                                                    |    |

|      | lator                                                                                                                                 | 94 |

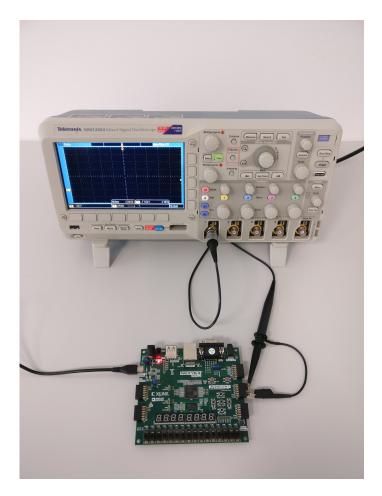

| 4.29 | Experimental setup for the hardware measurement                                                                                       | 96 |

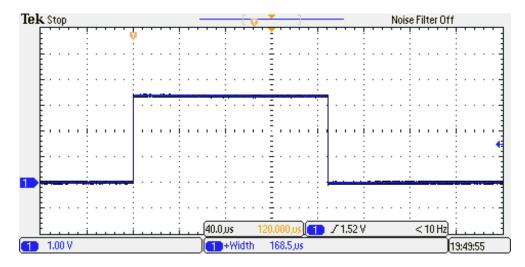

| 4.30 | Measurement of the processing time of the kernel with the proposed                                                                    |    |

|      | accumulator implemented on the FPGA                                                                                                   | 97 |

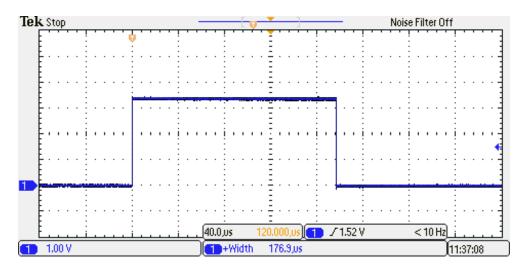

| 4.31 | Measurement of the processing time of the kernel with Simulink IP                                                                     |    |

|      | implemented on the FPGA                                                                                                               | 97 |

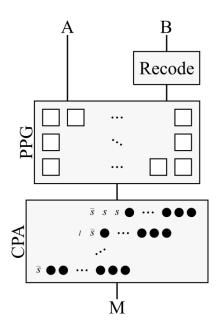

| 4.32 | Posit multiplier basic elements                                                                                                       | 99 |

v

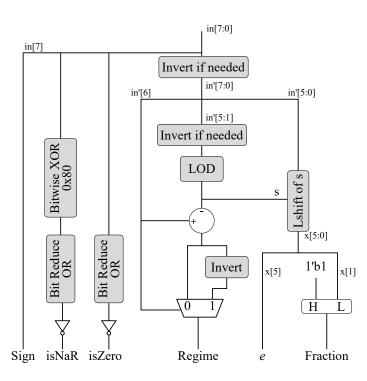

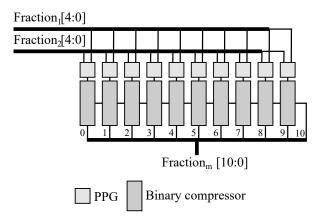

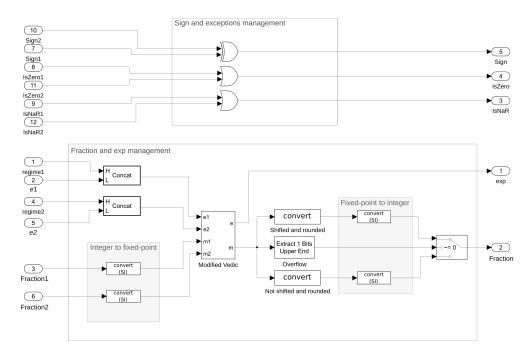

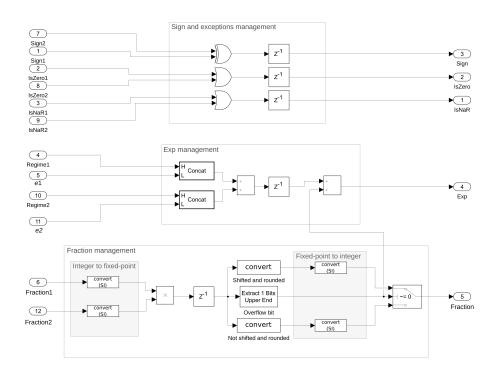

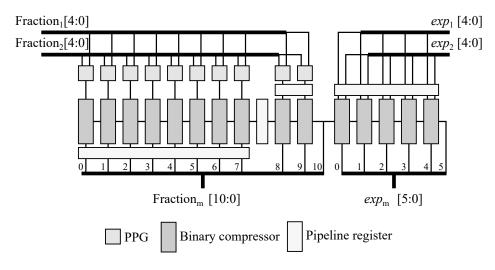

| 4.33 | Posit multiplier decoding block.                                            | 102 |

|------|-----------------------------------------------------------------------------|-----|

| 4.34 | Posit multiplier encoding block.                                            | 103 |

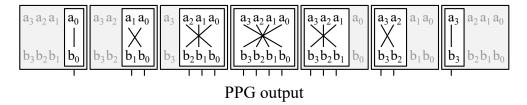

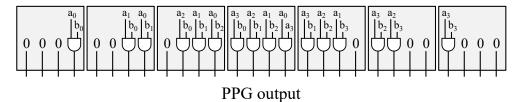

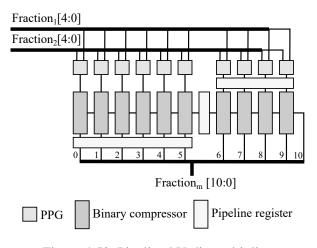

| 4.35 | Partial product generation with Vedic "vertical and crosswise" pattern.     | 104 |

| 4.36 | Vedic PPG with AND gates.                                                   | 104 |

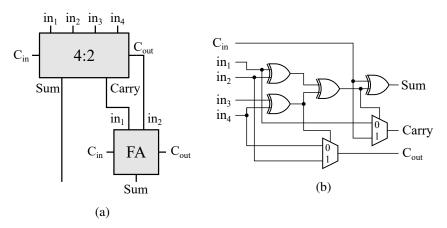

| 4.37 | Vedic adder elements: (a) 4:2 compressor coupled with a FA, (b) cir-        |     |

|      | cuit of a 4:2 compressor.                                                   | 105 |

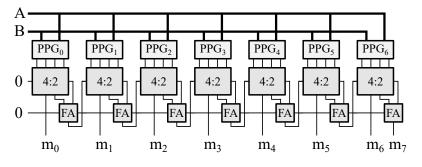

| 4.38 | Complete 4-bits Vedic multiplier                                            | 105 |

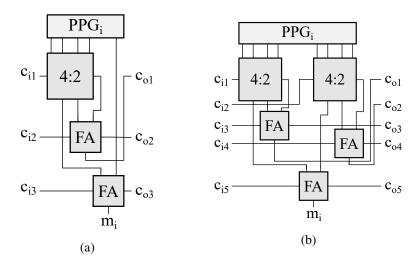

| 4.39 | Example of stages for (a) 5-bit and (b) 8-bit Vedic architectures           | 106 |

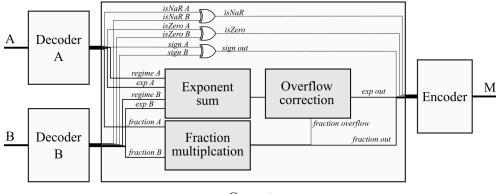

| 4.40 | Posit multiplier exponent exp sum, fraction multiplication, and ex-         |     |

|      | ception and sign management.                                                | 107 |

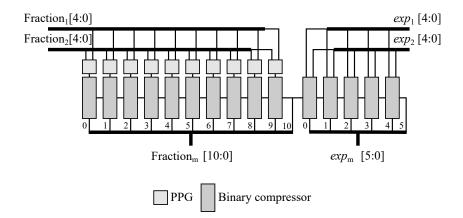

| 4.41 | 5-bits Vedic multiplier basic blocks to be used for a Posit(8,1) multi-     |     |

|      | plier system.                                                               | 108 |

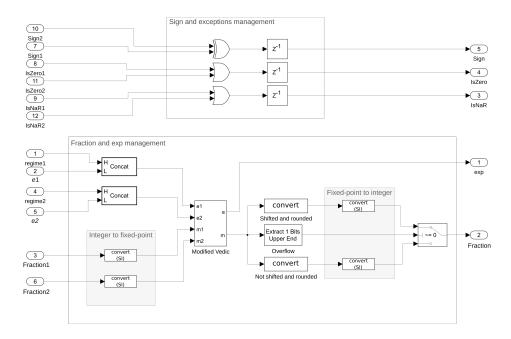

| 4.42 | Posit multiplier exponent exp sum, fraction multiplication, and ex-         |     |

|      | ception and sign management.                                                | 109 |

| 4.43 | Modified Vedic multiplier-adder, designed for 5-bit input fractions         |     |

|      | and 5-bit input exponents <i>exp</i>                                        | 109 |

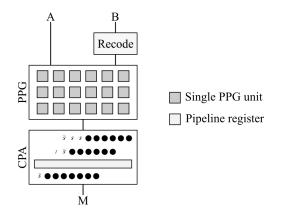

|      | Booth radix-4 multiplier basic blocks.                                      | 112 |

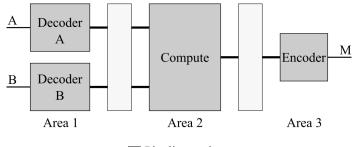

| 4.45 | Posit multiplier pipeline subdivision to isolate Decoder, Compute,          |     |

|      | and Encoder areas.                                                          | 113 |

| 4.46 | Posit multiplier pipeline subdivision to isolate decoder, compute and       |     |

|      | encoder areas, and to break down the compute area                           | 113 |

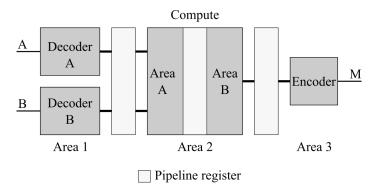

| 4.47 | Pipelined compute block when the Booth radix-4 multiplier is used.          |     |

|      | The pipeline registers are modeled in Simulink with the <i>Delay</i> block, |     |

|      | here represented with the $z^{-1}$ symbol                                   | 114 |

|      | Pipelined Booth radix-4 architecture basic blocks                           | 115 |

|      | Pipelined compute block when the Simulink default multiplier is used.       |     |

|      | Pipelined Vedic multiplier.                                                 | 116 |

| 4.51 | Pipelined compute block when the Modified Vedic multiplier-adder            |     |

|      | is used                                                                     | 117 |

| 4.52 | Pipelined Modified Vedic multiplier-adder                                   | 117 |

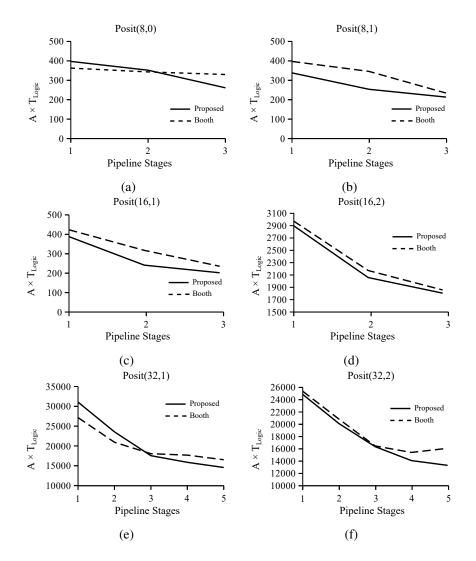

| 4.53 Comparison of the Posit multiplier with the proposed and the Booth |         |  |  |  |  |  |  |     |

|-------------------------------------------------------------------------|---------|--|--|--|--|--|--|-----|

| sol                                                                     | utions. |  |  |  |  |  |  | 121 |

# **List of Tables**

| 3.1  | Definition of True Positives (TP), True Negatives (TN), False Posi- |    |

|------|---------------------------------------------------------------------|----|

|      | tives ( <i>FP</i> ), and False Negatives ( <i>FN</i> ).             | 42 |

| 4.1  | Activity set                                                        | 49 |

| 4.2  | Activity sequence for each acquisition                              | 50 |

| 4.3  | Features used as the SVM input.                                     | 53 |

| 4.4  | Comparison of the training of the SVM algorithms                    | 53 |

| 4.5  | Implementation results on a Altera Cyclone IV                       | 69 |

| 4.6  | State-of-the-art hardware accumulator architectures                 | 75 |

| 4.7  | Main Control Logic working behavior.                                | 78 |

| 4.8  | Main Control Logic working behavior.                                | 79 |

| 4.9  | Post-implementation resources usage report generated by Xilinx Vi-  |    |

|      | vado                                                                | 82 |

| 4.10 | Simulink accumulator resource usage, maximum frequency, and la-     |    |

|      | tency on Xilinx Artix 7                                             | 89 |

| 4.11 | Simulink accumulator resource usage, maximum frequency, and la-     |    |

|      | tency on Altera Cyclone 10 LP                                       | 89 |

| 4.12 | Post implementation accumulator resource usage, maximum frequency,  |    |

|      | and latency on Xilinx Artix 7 FPGA                                  | 91 |

| 4.13 | Post implementation kernel resource usage and maximum frequency     |    |

|      | on Xilinx Artix 7 FPGA.                                             | 95 |

| 4.14 | Pseudocode of the LOD algorithm developed in [134]. N is the bit-                 |     |

|------|-----------------------------------------------------------------------------------|-----|

|      | size of the input <i>in</i> , S is equal to $log(N)$ , K is the output value, and |     |

|      | <i>vld</i> is the control signal used in the cascade of the blocks                | 101 |

| 4.15 | Summary of the compared algorithms to perform Posit multiplication.               | 118 |

| 4.16 | Implementation result of the combinatorial versions                               | 118 |

| 4.17 | Implementation result of the 2-stage pipeline versions                            | 119 |

| 4.18 | Implementation result of the 3-stage pipeline versions                            | 119 |

| 4.19 | Posit formats and pipeline stages taken into consideration for the                |     |

|      | comparison                                                                        | 120 |

<u>X</u>\_\_\_\_\_

# Introduction

Among the trending topics of the last years, the *Internet of Things* (IoT) is one of those gathering the most attention [1]. In its golden-rule implementation, this paradigm pursues the ubiquitous exchange of information between every kind of object, even those we nowadays perceive as the most irrelevant. Within this vision, the amount of data collected and produced by our actions should allow for building a better society, in which new services can be introduced to foster tailored healthcare and increasing well-being [2].

Although the final implementation of this conception may be perceived as utopian by most, we are slowly getting in touch with it in our daily lives. In recent years, the *Smart Home* concept has been extended from the simple automation and automatic control of the home appliances to more complex management of the user interaction with several sensors and actuators deployed in the home environment in order to pursue the users' well-being and energy sustainability [3, 4, 5, 6, 7, 8, 9, 10, 11]. Besides, the amount of data produced by users inside their own home environment can enable useful applications in health management, such as the early detection of behavioral trends and anomalies otherwise impossible to identify [12, 13, 14, 15, 9, 16, 17].

This new scenario requires a new generation of devices to be developed [18], aiming at gathering relevant information on how and when the user interacts with the home environment. One of the best ways to accomplish this task is to exploit both *environmental* (e.g. armchair sensors to monitor inactivity periods, toilet proximity sensors, etc.) and *wearable* (e.g. a device to be worn at the waist) sensors. In addition,

if those devices are able to send the collected data over the Internet, data can be processed and accessed by the various professionals involved (e.g. medical doctors, caregivers, relatives, and the users themselves) to give the best user-centered service.

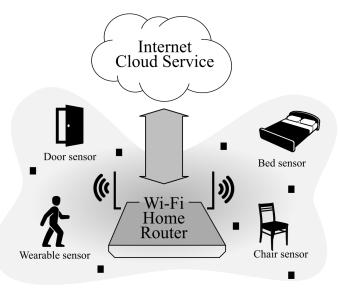

At the D2Lab of the University of Parma, a new home monitoring system has been developed to enable the behavioral analysis of the users inside their homes. Its working principle relies on a set of battery-powered sensors connected to an Internet cloud service (Figure 1). The sensors are responsible for gathering information about the user's actions inside the home and, at the end of the day, for sending it on the cloud for the analytics. It is important to notice that the system is not conceived for real-time reporting, but instead, it aims at providing a set of daily, weekly or monthly behavioral analyses to the user (or to who is in charge for her/him). This is required to highlight variations on user's macro- and long-term patterns (e.g. a decrease in mobility), and to act with specific prevention programs.

Figure 1: Sensors system for behavioral analysis.

Differently from traditional systems featuring low-power, low-cost wireless transmission protocols (e.g. Zigbee [19, 20, 21]), this system relies on Wi-Fi connectivity. If on the one hand the low-power protocols simplify the energy management of the

#### Introduction

IoT nodes, on the other hand they require completely new and dedicated infrastructure in each home in which the system is to be deployed, since, typically, a network compliant with these standards is not already there. Moreover, these low-power protocols feature a short area coverage and require a set of repeaters and range extenders to operate across multiple house rooms. These problems can be addressed by using the Wi-Fi protocol, which features a wider area coverage and whose deployment is simplified by exploiting a standard Wi-Fi home router (quite often already present in the homes) for the Internet connection. The result is a more scalable and less expensive final implementation.

This, of course, comes at the expense of increased power consumption, which may harm the sensors' battery lifetime. For this reason, dedicated sensor platforms have been designed at the D2Lab for low-power operation even on Wi-Fi connectivity. An extensive account for the exploited design methodologies is given in [22], where it is shown that the obtained battery lifetimes are suitable for practical exploitation.

Based on such studies, a complete set of specific environmental sensors have been developed, providing expressive information relevant to behavioral inference [3]: a magnetic contact, to sense the opening/closing of drawers or doors; an armchair/bed pressure sensor to detect the presence of the user on chairs or beds; a Passive InfraRed (PIR) sensor to reveal the presence of a person inside a room, calibrated to exclude small-size pets and animals (e.g. cats or small dogs); a toilet proximity sensor, to catch the user's interactions with the toilet service. The data collected by the sensors are sent to an IoT cloud platform for processing and visualization.

Moreover, the capabilities of the system have been extended with the introduction of a wearable sensor for Human Activity Recognition (HAR) to enrich the behavioral analysis with activities difficult or impossible to detect with environmental sensors [23, 24]. The design of the sensor required the same energy-aware techniques to be used, with particular care to the on-off cycles of the Wi-Fi radio. Typically, HAR algorithms rely on high sample rates of the motion sensors (e.g. 50Hz [25]), whose data need to be processed to extract the activity of the user. In this specific case, if all the computation part was on the cloud, the Wi-Fi radio would be continuously uploading the stream of data, negatively affecting the battery lifetime. For this reason, provided that the energy required for computational activity is much less than that dissipated by the radio, a part of the computation needs to be moved on the wearable device to send on the cloud just the final activity of the user. In particular, a machine learning algorithm has been selected and studied for this application.

This is the context of this thesis, which is focused on the study and further development of the aforementioned behavioral analysis ecosystem. The aim is to build a system capable of addressing the main trade-offs of the state-of-the-art, namely behavioral analysis complexity and battery power efficiency. To reach this goal, a performance assessment and optimization of the environmental sensors have been carried out, and the design and development of the wearable sensor have been performed.

After the first part of related works (chapter 1) and background (Chapter 2), a work on the set of environmental sensors has been carried out in Chapter 3 for performance assessment. Then, in Chapter 4, the design of the wearable sensor for HAR is presented, which led to the study of the algorithm and the hardware for the application.

### **Chapter 1**

## Background

This Chapter is a collection of the theoretical notions this thesis relies on. The concepts described here will then be exploited for the experimental parts of this work.

#### 1.1 Support Vector Machine Algorithms

A Support Vector Machine (SVM) is a machine learning algorithm that, in its simplest form, can solve a binary classification problem using two or more input values called *features* [26]. For example, let us imagine having to distinguish if an object is "an apple" or "not an apple" based on the weight, height, width, and color of the object. In this case, we can plan to use this set of information as the *features* (i.e. the input) of an SVM algorithm to obtain at the output the *classification* of the object in the "apple" or "not apple" class.

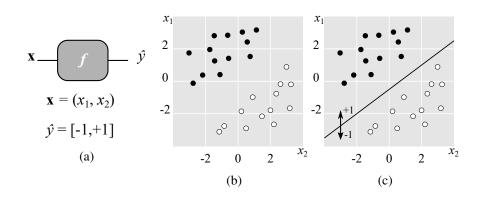

To formalize this concept, let us take the case of two generic input features  $x_1$  and  $x_2$  of Figure 1.1a (i.e. the *features space*). The aim of the algorithm is to provide an output label  $\hat{y} = +1$  or  $\hat{y} = -1$  whether the current input features vector x is of the same set of the black or the white dots, respectively (Figure 1.1b). In other words, it tries to *classify* the new input x relying on the information already known by the algorithm, i.e. the black and white dots provided in the *training* phase.

To do so, the algorithm makes use of a threshold line as shown in Figure 1.1c.

Figure 1.1: Support Vector Machine linear example: (a) input-output function, (b) features space, (c) features space with threshold line.

If the features input vector  $\mathbf{x} = [x_1, x_2]$  is above the line in the features space, it is classified as +1, if it is below the line, it is classified as -1. This is exactly the aim of such systems: to classify an input into the proper output class.

Diving deeply into mathematical details, when dealing with a linear classifier as in the example, the equation used for the function f is

$$f(\mathbf{x}) = sign(\langle \mathbf{w}, \mathbf{x} \rangle + b) = sign\left(\sum_{i} w_{i} \cdot x_{i} + b\right), \qquad (1.1)$$

where  $\langle \mathbf{w}, \mathbf{x} \rangle$  is the dot product of the input features vector  $\mathbf{x}$  and a vector of weights  $\mathbf{w}$ , and b is a bias term. In two dimensions, this equation is exactly the equation describing a line on a plane and, indeed, it is the line defined in the features space. At every new input  $\mathbf{x}$ , the equation is solved and the *sign* function detects whether the input point is below or above such line.

As shown in Figure 1.1c, the key aspect for a proper classification is the position of that line, which must separate exactly the points already present on the plane. For this reason, the training phase is used to find the best equation for f.

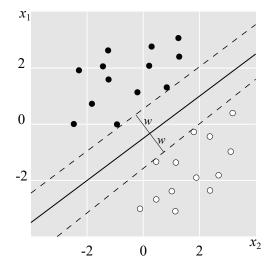

During the training phase, the training algorithm iteratively aims at finding the best  $\mathbf{w}$  and the *b* which maximize the *margin* between the points already known by the system (i.e. the training set) and the line, as shown in Figure 1.2. The set of

weights w defining the separation of the features space are called *support vectors*.

Figure 1.2: Best fitting threshold line.

Those techniques allow us to define the so-called Linear SVM classifier.

#### 1.1.1 Kernelized Support Vector Machine

The Linear SVM classifier is efficient enough until the classification problem is simple and the feature space is linearly separable or close to linearly separable. However, in reality, many classification problems are not that easy and it may be difficult (if not impossible) to perform the optimum separation.

In such cases, the solution to the classification problem can still be achieved by using a *transformation* of the features space in order to switch to a new space where the classes can easily be separated. The transformation is performed by applying a function, called *kernel*, to be used in place of Equation 1.1 with

$$f(\mathbf{x}) = sign(\langle \mathbf{w}, k(\mathbf{x}, \mathbf{w}') \rangle + b), \qquad (1.2)$$

where **w'** is the weights vector transformed in the kernel space [27], and  $k(\mathbf{x}, \mathbf{w}')$  is the kernel function.

Several equations are used in literature for the kernel function depending on the problem to solve. For reference, here are reported the most frequently employed:

- Polynomial:  $k(\mathbf{x}, \mathbf{w}') = (\langle \mathbf{w}', \mathbf{x} \rangle + c)^n$ , where *n* is the polynomial degree;

- Gaussian or Radial Basis:  $k(\mathbf{x}, \mathbf{w}') = exp(-\gamma ||\mathbf{x} \mathbf{w}'||^2)$ , where  $\gamma$  is a positive, non-zero constant;

- Sigmoid:  $k(\mathbf{x}, \mathbf{w}') = \tanh(\gamma \cdot \mathbf{x}^T \cdot \mathbf{w}' + b)$ .

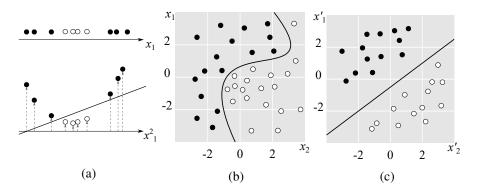

To better understand the effect of this solution, let us take a single-feature example of the top Figure 1.3a.

Figure 1.3: Kernelized Support Vector Machine example: (a) single-feature linear (top) and kernelized (bottom) example, (b) original input feature space with kernelized threshold, (c) kernelized input feature space.

In this case, it is clear that a linear separation (which should be done using a vertical line) of the black and white classes is not possible. However, the solution here can still be obtained by transforming the feature space as the bottom Figure 1.3a, in which the  $x_1$  axis is squared to introduce a new feature  $x_1^2$ . With this new configuration, the points of the features space rely on a paraboloid instead of a straight line, and the separation turns to be feasible with the same techniques of a linear classifier.

This concept can also be extended to the 2-features example of the previous Section. Figure 1.5b shows again a features space impossible to be linearly separated. However, by using a *cubic polynomial kernel*  $k(\mathbf{x}, \mathbf{w}') = (\langle \mathbf{w}', \mathbf{x} \rangle + c)^3$ , the original features space can be separated and transformed in the new features space of Figure 1.3c.

When using a kernel function to move to another features space, it is suggested to normalize the features using the information acquired during the training phase. In fact, any small out-of-scale which would not affect a linear SVM algorithm, may produce considerable effects in a kernelized implementation due to the amplification introduced by the kernel function.

This means applying the following standard score statistical normalization equation:

$$\mathbf{x}_{norm} = \frac{\mathbf{x} - \boldsymbol{\mu}}{\boldsymbol{\sigma} \cdot \boldsymbol{s}},\tag{1.3}$$

where  $\mu$  is a vector of mean values,  $\sigma$  is a vector of standard deviation values and *s* is a vector of scale values. The output  $\mathbf{x}_{norm}$  is the normalized features vector to be used in place of  $\mathbf{x}$  in Equation 1.2.

#### 1.1.2 Multiclass Problem

In the real world, it frequently happens that more than two classes need to be distinguished at the output. Although the base SVM algorithm only deals with binary classification problems, multiclass problems can be managed by combining more than one SVM algorithms together. If *m* output classes have to be classified, two techniques are possible: *one-to-one*, requiring m(m-1)/2 binary classifiers, and *one-to-rest*, requiring *m* binary classifiers.

The one-to-one approach performs the classification in pairs and, in the end, the class with the higher score is used as the final output. The one-to-rest approach instead uses the classification of one class among all the rest of the dataset, actually classifying the class or the non-class. The class which has obtained the highest score is then selected as the final output.

The usage of one technique in place of the other depends on the application requirements.

#### **1.2 Model-Based Design**

This Section is about the model-based technique, which has been used as the workflow for the development of the SVM core described in Chapter 3.

The design flow of dedicated hardware architectures is traditionally done by starting with a handwritten Hardware Description Language (HDL) and, after subsequent testing and verification methods, the system is implemented on the destination platform (e.g. MCU or FPGA). However, when dealing with complex systems or in large-scale projects this can be a challenging task, especially if the documentation and requirements collection phases address totally different topics than the hardware design and implementation ones. In fact, in such cases, the workflow must be flexible enough to allow information to flow from the design part to the software/firmware part, and vice versa.

The common way to achieve this task is to produce a set of document-based requirements (which may also be carried out by a separate design team) to be used in the final implementation part (which may also be carried out by a separate software/firmware team). Then, after the implementation, tests are carried out to verify if the requirements were fully and correctly designed for the application. In case of a testing failure, the process goes *backward* to the implementation phase and, if no issues are detected, it goes back further to the design phase. Then, after the corrections, the whole *forward* flow is repeated until both the requirements and the implementation are free of issues.

This trial-and-error approach may be enough for simple or standalone applications, however, if the complexity of the system grows, more design iterations are to be expected, and the waste of time of this methodology can turn to be consistent [28, 29]. As proved by different works [30, 31], dealing with model-based frameworks can help all the phases involved in the process. On the one side, the design phase can benefit from the advanced testing tools offered in the design environment, easing the requirements simulation and verification, and experimenting with virtually limitless ideas and designs. On the other side, the implementation phase can benefit from the code generation tools usually included in such model-based frameworks, which can automatically translate the functionality of the design phase to a verified low-level code (i.e. C, VHDL, etc.). This can eliminate the time-consuming, errorprone handwriting phase.

#### 1.3 Posit Numbers Theory

In this Section, the Posit numeric format is introduced to understand the theoretical background on which the final part of Chapter 3 relies on.

The Posit format is a numeric data type conceived as a drop-in replacement of the IEEE 754 floating-point standard and which aims at providing an increased dynamic range with the same representation bits [32].

Compared to the IEEE 754 standard, using a Posit representation gives several advantages, such as a reduced accuracy loss, a higher dynamic range and, a Not-a-Real (NaR) notation which substitutes the infinity to avoid overflows or underflows [33].

Posit numbers have the following general binary representation:

Figure 1.4: Bit-field representation of a Posit number.

where S, R, E, and F are the sign, regime, exponent, and fraction fields, respectively, with their lengths reported on top. The total length of the Posit representation is indicated with n.

The sign field S is always the most significant bit of the Posit bit-string. Its meaning matches the IEEE 754 format, with a 0 and 1 indicating a positive or negative sign, respectively. The regime field is a sequence of bits starting with r bits of the same value (0 or 1) terminated by a bit of opposite value. As an example, a regime bit sequence can be "000001", "1110", "01", etc. To be used in computations, this field needs to be converted to an integer value with the following equation:

$$k = \begin{cases} -r, & \text{if string starts with 0} \\ r-1, & \text{if string starts with 1} \end{cases}.$$

(1.4)

where k is the integer regime value. The exponent field is different from the exponent definition of the IEEE 754 format. To extract the equivalent exponent value to be used in computations, the following equation needs to be used:

$$exp = 2^{es+k} \cdot e \tag{1.5}$$

where exp is the integer exponent value and e is the integer value represented in the E field. In other words, the exponent exp is the result of the concatenation of k as the high part and e as the low part. In this thesis, e will refer to the Posit exponent bit-field value and exp to refer to the converted value to be used in the computations shown in the following Sections.

The fraction field has the same definition as in the IEEE 754 format: by adding the hidden 1 at the most significant bit, the fraction is directly represented as a 1.F fixed-point number. The real decimal value N of the Posit number can be found with the equation

$$N = (-1)^S \cdot 2^{exp} \cdot 1.F \tag{1.6}$$

When referring to the Posit numbering system, the notation used embeds information about the size of *n* and *es* fixed fields:

$$Posit(n, es) \tag{1.7}$$

As an example, the notation Posit(8,1) refers to a Posit format with numbers of 8 bits, of which 1 bit is for the exponent e.

#### 1.3.1 Regime Variable Length

The key concept of Posit numbers is the regime field R, which has been designed to have a *variable* bit length r. Since the Posit total size n is fixed, having a longer sequence of regime bits translates in "stealing" bits from the exponent e and the fraction fields, which are then pushed to the right and outside of the Posit representation. In the extreme case, the regime field can extend to push out both the exponent e and the fraction, which are then considered filled with zeros. This property allows us to "tune" the accuracy of the binary representation of the number by acting on the regime string.

Let us consider two cases of real numbers representation: a number close to 1 and a number close to the maximum value allowed by the dynamic range. In the first case, the exponent *exp* is not needed and all the relevant information will be carried by the fraction part. Hence, a high number of fraction bits is required. However, in the second case, the situation is opposite because this time the relevant information is carried by the exponential notation. The fraction part can be neglected and all the bits should be dedicated to the exponent *exp* part.

If the number of total bits n is fixed, the Posit numbers can achieve better performance than the IEEE 754 format in both situations because they can move the bit depth where more information is needed thanks to the variable size of the regime field (which concurs to the final *exp* value as shown in Equation 1.5).

Another outcome of the Posit format is the resource saving. If the project constraint of the application is the accuracy and the dynamic range, the Posit numbers can nearly reach IEEE 754 performance while needing half of the representation bits, as shown in [34]. The result is that, if using Posit numbers, the computational load can be lowered while still having a comparable representation quality.

#### 1.3.2 Special Cases

As aforementioned, the Posit standard also identifies two special cases: *NaR* and *Zero*. They have special encodings which must be detected to produce the correct result during operations. In particular, the NaR case is encoded as a Posit string starting

with 1 and followed by all 0 and the Zero case is a string of all zeros.

### Chapter 2

### **Related Works**

In this Chapter, the state-of-the-art related to this thesis work is presented.

#### 2.1 Smart Home Systems

The concept of a Smart Home has evolved remarkably over the past few decades. Initially, the Smart Home coincided with Home Automation intended as technological solutions applied to the home environment to automatically manage some situations (e.g., open doors/curtains, control thermostat) and detect dangerous events (e.g., fire, flood), freeing the user from manual control [35]. Now, the evolution of ICT (Information and Communication Technologies) has allowed for the addition of many advanced features to smart homes over time, extending the possible applications. Among the advancements, the monitoring of human activity in the home environment has particular importance. Modern systems exploit human monitoring mainly to improve the energy management of the building [36, 37, 38, 39, 40, 41]. However, data related to the users and how they live in their own home environment can find straightforward applications in health management, allowing for early detection of behavioral trends and anomalies possibly relevant to one's well-being [12, 13, 14, 15, 9, 16, 17].

To accomplish this task, some new devices have to be developed [18] aimed at

considering the interaction of the user with the home environment (e.g. armchair sensors to monitor inactivity periods, toilet proximity sensors, etc.). These devices must be able to send data over the Internet so that, once processed, they can be accessed by the various professionals involved, for example, medical doctors, caregivers, relatives, and the users themselves.

Applications based on such a system have been presented in past works. For example, an infrastructure based on a Passive InfraRed (PIR), bed and temperature sensors were reported in [42]. In this case, the data transmission was based on the X10 wireless protocol, and a home server was exploited to process data and to send analyses and alerts to a third person (i.e. the clinician) through emails. Another monitoring system based on temperature, pressure, PIR sensors, and actuators was described in [43]. Sensors communicated with a local computer by means of a wireless ZigBee protocol. Data were processed to monitor the activities of elders, and the results determined which actions to take. The system proposed in [44] leans on a mix of ZigBee and Power Line Communication (PLC) transmission protocols. The architecture was conceived with distinct ZigBee Wireless Sensor Networks (WSNs) in each room, which communicate with a central management station through a PLC. An infrastructure exploiting a custom wireless protocol, the so-called Wellness protocol, was presented in [45]. The implementation was based on temperature, pressure sensors, PIR sensors, a manual alert button, and actuators. Another example of such a system was CARDEA (Computer-Aided, Rule-based Domestic Environment Assistant), developed at the University of Parma and specifically aimed at behavioral analysis. Originally based on the Ethernet protocol [46, 47], the system's strength is flexibility. It is conceived to integrate different kinds of sensors and to support smart interfaces [48, 49], in order to tailor the system's functions to the specific users' needs. By supporting a wireless protocol (i.e. IEEE 802.15.4/ZigBee) as well, further kinds of devices were introduced; the most remarkable is the wearable sensor MuSA (MUltiSensor Assistant) [50, 51, 52, 53], designed for user motion analysis (e.g. fall monitoring) and for localization and identification purposes [54, 8].

Most of the systems presented in the literature based their connectivity on wireless protocols featuring low-cost hardware and low power consumption (e.g. ZigBee [19, 20, 21]). Coupling the low power required by a ZigBee transmission with recent developments in the field of energy harvesting, it is now possible to develop batteryless IoT nodes [55, 56]. However, powering the ZigBee protocol tasks for prolonged periods of time (i.e., >10 s) with energy harvesters is not recommended [57]. Some advanced functions (e.g. localization or identification [58]), useful in Smart Home systems conceived for the continuous monitoring of the individuals and for behavioral analysis, are likely to be prevented. Moreover, the disadvantage of the ZigBee (or low-power equivalents) approach is mainly the necessity of completely new and dedicated infrastructure in each home in which the system is going to be deployed, since, typically, a network compliant with these standards is not already present. Furthermore, a gateway device has to be considered as an interface between the home protocol and the Ethernet, in addition to a number of range extenders due to the low range featured by ZigBee [59].

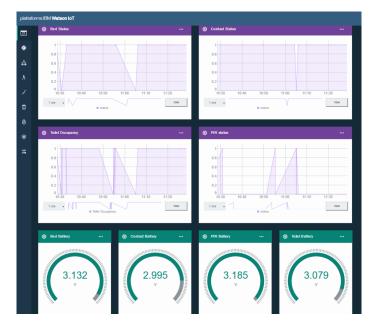

In the D2Lab research group of Electronic Engineering at the University of Parma, a new home monitoring system entirely based on Wi-Fi connectivity has been developed, in a fashion strictly compliant with the Internet of Thing (IoT) paradigm. Sensors connect to the Internet through a standard Wi-Fi home router, which is quite often already present in the homes. Some manufacturers are already producing chips for routers able to support Wi-Fi, Bluetooth, and ZigBee protocols in parallel (e.g., Qualcomm QCA4020 and QCA4024 [60]). These solutions could simplify the adoption of multiple protocols in the near future, but do not eliminate the need for building a complete infrastructure for the ZigBee sensors and in particular for deploying range extenders in the environment. On the contrary, Wi-Fi features a much wider range than ZigBee, so that no (or fewer) network extenders are needed, simplifying the overall approach, lowering the costs, and making the whole system more scalable. These characteristics open the system to the market, making it particularly attractive to consumers. This, of course, comes at the expense of increased power consumption, which may harm battery lifetime. Therefore, dedicated sensor platforms have been carefully designed at D2Lab for low-power operation composed of both environmental and wearable sensors. The general system architecture is sketched in Figure 2.1. It includes a set of sensing devices, a Wi-Fi router, and services installed on a cloud

environment. Currently, it exploits the IBM Bluemix Watson IoT platform (although other cloud services are supported, e.g. Amazon AWS, Microsoft Azure, MathWorks Thingspeak, etc.), which offers a dashboard that enables a handy visualization of sensors information, as shown in Figure 2.2.

Figure 2.1: Wi-Fi system architecture.

#### 2.2 State of the Art in HAR

Nowadays, human activity recognition is a subject of research interest because of the benefits it can bring in several fields, i.e. sport, health, security, etc. Several research groups realized and tested novel approaches to achieve better performance and/or lower costs mainly following two paths: hardware and firmware/software solutions. These are two sides of the same coin because the optimization of one gives positive results in the development of the other and vice versa.

In this Section, the state-of-the-art is reported to figure out the current advancements on this topic. Starting from the wider point of view of HAR, the research is organized to end with a closer look at HAR with wearable devices. In this journey, a view on embedded hardware and firmware/software solutions is also given to have an idea of how the literature is moving on these fields.

Figure 2.2: IBM Bluemix Watson dashboard reporting Wi-Fi sensors activity and battery level.

As a starting point, the best way to have an idea of the landscape is to analyze review works on this subject. In [61], the team resumes the state-of-the-art in the activity detection and classification field exploiting wearable devices. The study is mainly focused on the hardware type (accelerometer, gyroscope, magnetometer, camera, audio, electrocardiography (ECG), photoplethysmographic (PPG), etc., along with their location), algorithms employed (decision tree, SVM, K-Nearest Neighbor (KNN), etc.) and activities recognized (sitting, standing, walking, etc.). The result is an identification of a set of research works that have been summarized and classified by type of sensor (accelerometer/gyroscope/magnetometer, camera, or hybrid), number of used sensors, number of subjects used for testing, and type of classification learner employed (threshold, unsupervised, supervised).

In [62], Hooshmand et al. review the state-of-the-art algorithms used to lossily compress bio-signals with the aim to evaluate the best approach to realize efficient

energy saving in wearable devices. The study considers 1-D bio-signals such as ECG, heart or respiratory (RESP) rates, and PPG. It presents novel approaches based on online dictionaries, elucidating their operating principles and providing a quantitative assessment of compression, reconstruction, and energy consumption performance of all schemes. In the end, the team considers the most efficient schemes the ones which allow for reducing the signal size up to 100 times, entailing similar reductions in the energy demand while still keeping the reconstruction error within 4% of the peak-to-peak signal amplitude.

#### 2.2.1 Hardware Solutions

The hardware side of a HAR system can be identified by both the sensing parts involved in raw data collection and the processing parts dedicated to data processing. Depending on the final applications, these two components can reside on the same device (e.g. MuSA [52], a wearable sensor that signals a detected fall) or can be two or more distinct devices (e.g. SmartShoe [63], a shoe that sends raw data to the smartphone for energy expenditure calculation). In the second case, the hardware dedicated to the processing phase can be treated as ideal, typically being a system with a high amount of processing power to make this computational effort negligible. The first case is instead the most challenging one, as it is the configuration that provides ubiquity but, at the same time, forces to deal with physical size, battery lifetime, and computing capability.

In literature, several systems are presented, each one proposing the better tradeoffs for the application.

In [64], a monitoring system based on muscular activity is presented. This is commonly done by electromyography (EMG) systems, a precise method but too sensitive to environmental disturbances. Here, the new exploited method relies on air-pressure sensors and air-bladders. Since the change of the air pressure can be more robustly measured compared with the change of skin electric signals, the proposed sensing method is useful for mobile devices due to its great signal-to-noise ratio (SNR) and fast response time. In the paper, the research group verified the performance of the system by comparing it with an EMG signal and motion sensor. A totally different approach was adopted in [65], in which a monitoring system able to perform activity recognition by monitoring changes in Wi-Fi signals (hence without a device that needs to be worn) is presented. The method exploits a Channel State Information (CSI)-based Human Activity Recognition and Monitoring system, called CARM. This is a merge of two models: the first is based on a CSI-speed model that quantifies the relation between CSI dynamics and human movement speeds, the second is a CSI-activity model that quantifies the relation between human movement speeds and human activities. This system has been tested with the implementation on commercial Wi-Fi devices and, after the analysis of True Positives (*TP*), True Negatives (*TN*), False Positives (*FP*), and False Negatives (*FN*), the group achieved the recognition accuracy of Equation 2.1.

$$Accuracy = \frac{TP + TN}{TP + TN + FP + FN} = 96\%$$

(2.1)

Similarly to [65], the work presented in [66] is about PAWS (Passive Human Activity Recognition Based on WiFi Ambient Signals) in [66], an indoor localization system. It uses the RSSI fingerprint of different activities to perform activity recognition in a Wi-Fi environment. To reach the goal, a novel fusion algorithm has been specifically designed based on the classification tree, resulting in an outperform of three other well-known classifiers in terms of accuracy and complexity: NaiveBayes, Bagging, and KNN. The group presented a first prototype version for tests in real-life conditions.

In [67], the work focuses again on device-free wireless activity recognition and localization with the aim to simplify the characterization of the target, a key aspect to increase the accuracy of the recognition system. The solution here was to apply a sparse auto-encoder network algorithm for wireless features discrimination and then, with the selected features, a softmax-regression-based machine learning framework was used. This enables the system to simultaneously perform location, activity, and gesture recognition with an accuracy of 85%. This value is proved to be higher than what was obtained by systems using traditional handcraft features.

Another indoor device-free activity recognition technique has been studied in [68]. Leveraging the subject and analyzing the non-line-of-sight (NLOS) radio fre-

quency signals, a KNN classifier algorithm has been used on the packet receive rate to recognize the activity of a person. They also found that the radio frequency of the signal is proportional to the height of the person, so to extract that information too. With this method, the group achieved an average accuracy increase of 44% compared to the fixed-sample RSSI-based method and an accuracy of 76.6% in distinguishing the height of the moving target.

Wearable shoes (SmartShoe) are used instead in [69], which were equipped with pressure sensors and an accelerometer to analyze user movements. In the paper, the group focuses on a comparison between two classifiers (SVM and Multilayer Perceptron (MLP)) used for activity recognition, both with rejection. They find out a benefit using MLP, reaching a 99.8%±0.1% of accuracy.

As a development phase, in [63] the same group explores the feasibility of a system in which data acquired by the shoes are sent to a smartphone for the computation of the Energy Expenditure (EE) and to perform activity recognition. To test the best algorithm to use, they make a comparison between three classifiers: SVM, Multinomial Logistic Discrimination (MLD), and MLP. Tests have been carried out on 15 subjects and the result is that, despite the same accuracy given by all three methods (~95%), MLD and MLP require less running time and memory by a factor of more than  $10^3$  for activity recognition. No significant differences are present for EE.

With a similar sensing element (shoe) but with different addressees, [70] shows HAR applied to caregivers during their work. The aim is to detect possible overexertion injuries caused by awkward postures during patients handling. The group uses a smart wearable device (named Smart Insole 2.0) and a novel spatio-temporal warping pattern-recognizing framework. The results validation is done by a pilot study on eight subjects and an overall classification accuracy of 91.7% is achieved.

Another change in hardware occurs in [71], where the focus is on heterogeneous features learning for RGB-depth (RGB-D) activity recognition using a dedicated video camera. The group extracted similar hidden structures coming from each of the four channels and applied a joint learning model to explore shared and feature-specific components. The uniform system has been called "joint heterogeneous features learning (JOULE) and has been proved to successfully recognize human activ-

#### ity, focusing on human-objects interactions.

Coming to smartphones, [72] shows a performance analysis of an activity recognition system based on modern mobile phones. By analyzing sensory data sequences (form accelerometer, gyroscope, light sensor, proximity sensor, barometer, and GPS) of 10 subjects, the group assigns an F-score number to categorize performances under various placement settings (arm, hand, pocket, and waist). With the additional implementation of four different multi-class classifiers (linear and Radial Basis Function (RBF) kernel SVM, Random Forest, and KNN) they make a complete comparison of the techniques based on smartphones hardware.

A mixed approach between device-free and wearables is used in [73], in which a study of an activity recognition system based on Passive Radio-Frequency Identification (RFID) tags is presented. The idea is to use several RFID tags (which can be embedded on the clothes) and an RFID reader with two antennas, all worn by the user. This system is proved to be able to detect human motion by analyzing RSSI signals between tags and antennas. Data processing is performed in a dedicated online environment that provides the result with a latency of 5 seconds. The outcome is a non-invasive set of objects that, after two weeks of tests on four subjects, gave an accuracy of 93.6%.

The same RFID technology with a different application is used in [74]. The aim here is to perform activity recognition based on objects tracking, hence human-object interaction. The system relies on one or more RFID tags placed on the object to track, and several antennas placed around the room. Tracking is performed exploiting antennas signals trilateration based on RSSI information. In particular, a Gaussian Mean Weighting Filter is used to correct RSSI instability and Elliptic Trilateration is used to decrease the error given by the antenna not being omnidirectional. Results show an average activity identification of 93.3%.

A peculiar HAR system is then presented in [75], which introduces a floor embedding pressure sensors. They use piezoelectric sensors to get pressure information proportional to the user's gait and, with this particular technology, large areas such as train stations, hospitals, or shops can be covered. After some signal conditioning hardware, that set of information is sent to a central unit for data processing. They demonstrated the ability to recognize footsteps, jumps, sitting down into or standing up from a chair, and impact of objects with an accuracy of 100% using Pearson Product-Momentum Correlation Coefficients as a classifier.

In [52], the MuSA wearable sensor is introduced, with the ability to perform localization, identification and, exploiting its on-board sensors, fall detection, heartbeat, and breathing rate. The sensor is thought to be worn at belt or chest and, with the other sensors included in CARDEA environment [76], provides an ambient assisted living to support interaction between users and caregivers.

#### 2.2.2 Firmware and Software

In addition to hardware elements intended to sample and process data, a HAR system needs efficient algorithms to obtain the result. Raw data cannot directly provide information about human activity but must be modified by one or more algorithms dedicated and possibly optimized to retrieve certain information. Research on this topic teems of excellent works aimed to find the best approach to extract the information of interest, regardless of whether the goal is the computational speed, the accuracy, or the limited hardware.

In [77], the system performs activity recognition exploiting an accelerometer placed in different places: waist and ankle. Exploiting a ZigBee connection, the aim of this study is to find an optimized algorithm for this low-performance hardware and to increase independence from the sensor position. For data processing, the research group uses a novel Ensemble Empirical Mode Decomposition (EEMD) to identify the set of features and cooperation Game theory for features selection (GTFS). In the end, a consistent increase in accuracy is shown using the EEMD features and, using the GTFS, a significant reduction in the needed features is obtained.

A different HAR algorithm able to work with few labeled activity data and additional information from users (i.e. weight, height, etc.) is presented in [78]. So doing, the system can identify the fitness of others' models relying on a small amount of labeled data from the new user. Once placed the new user in the proper shared activity model, the algorithm uses Bayesian networks and SVMs to perform activity recognition. The result is an increase in accuracy (83.4% compared to 77.3% of individual and standard population models). Another aspect arising from this study is that this new method provides better results than methods based on users' demographic information.

A camera-based approach is used in [79], which describes a Fuzzy Segmentation and Recognition algorithm applied to video recordings of user's actions. The main focus is to be able to correctly recognize activities with gradual transitions between them. To do so, the algorithm performs a segmentation of the video into a sequence of non-overlapping blocks, each one lasting a short period of time. Then, multivariable time series are formed by concatenating block-level human activity summaries that are computed using topic models over local spatio-temporal features extracted from each block. After encoding the fuzzy event through Fuzzy Segmentation, the system can correctly apply an activity label with transitions. Results based on six datasets give an accuracy between 42.6% and 78.9%.

The work presented in [80] introduces the Interest Point features as an improvement in video input sequential modeling for action/activity recognition. To obtain the result, the algorithm first splits the video sequence into short overlapping segments of fixed size through a sliding window technique. As the second step, each segment is described by a local Bag Of Word (BOW) of the histogram of Interest Points (or their trajectories) enclosed in the segment. As the last step, a first-layer SVM classifier converts each BOW into a vector of class conditional probabilities that are then given as input to a second SVM (hidden conditional random field) for actual recognition. A comparison with state-of-the-art algorithms on three public datasets shows that this system can outperform or match each leader.

Referring to the same video activity recognition, [81] proposes a system that can recognize incoming visual content based on the previously experienced activities. The high-level activity is parsed into consecutive sub-activities, and a context cluster is built to model the temporal relations. The semantic attributes of the sub-activity are organized by a concept hierarchy. The dynamical evolution of the brain memory is mimicked to allow the input information to decay and reinforce, providing a natural way to maintain data and save computational time. Performances are tested by comparing this algorithm and traditional incremental learning method [82] on three public datasets (CAD-120, MHOI, and OPPORTUNITY). Results demonstrate the same accuracy with less time cost.

With the addition of depth information on the camera's signals, the work described in [83] shows a novel framework to be applied for HAR. The techniques employed are first an extension of the surface normal to polynomial by assembling local neighboring hypersurface normals to jointly characterize local motion and shape information and then a supernormal vector (SVN) scheme to aggregate low-level polynomials into a discriminative representation (such as a simplified Fisher kernel representation). To capture the spatial layout and temporal order, a subdivision of the depth video into a set of space-time cells is performed using an adaptive spatio-temporal pyramid. To make a comparison, a linear SVN solver is used on four public datasets and results are compared to state-of-the-art public HAR algorithms. An increase in accuracy of up to 3% is obtained.

In [84], the aim is to study the optimum classification method of accelerometer signals for Activity Recognition (AR) and Movement Recognition (MR) applied to rehabilitation and elderly monitoring. The work exploits an accelerometer of a smart-phone to recognize several activities (idle, still, walking, running, going up/down the stairs, or cycling) and movements (arm circles, arm presses, arm twist, curls, seaweed, and shoulder rolls). As a comparison, SVM, decision trees, and dynamic time warping classifiers are taken into consideration. Results show an accuracy above 90% in AR and above 99% in MR using SVM-based approaches.

Referring to Ambient Assisted Living (AAL) field, [85] focuses on the difficult task of estimating the required window for online sensory data streams (coming from a variety of sensors) to recognize a specific activity. The proposed solution is to split the problem into two phases. First, an Offline Phase is performed. Starting from an annotated training set and with the most relevant feature selected (in the study this is chosen among a number of activations of each sensor, activation duration of each sensor, number of activated sensors for each activity, and the location of the sensor), a matrix containing the best fitting sensor for each activity is calculated using Information Gain attribute evaluation [86]. The second step is an Online Phase. Here, an optimum window is calculated by checking if the current active sensor is contained in the best fitting matrix. The phase continues then with the extraction of the features to be used in the subsequent multi-class classification. After all these steps, the activity is given as result.

In the work presented in [87], the group proposes a bidirectional feature to be used during the features extraction phase of activity recognition. Because of the two components of a bidirectional feature, the problem can be treated as a second-order tensor. For this reason, the research group defines a new tensor-based feature selection method named Tensor Manifold Discriminant Projections (TMDP). It simultaneously applies an optimization criterion that can directly process the tensor spectral analysis problem, extracts local rank information by finding a tensor subspace that preserves the rank order information of the within-class input samples, and extracts discriminant information by maximizing the sum of distances between every sample and their interclass sample mean. Using Principal Component Analysis (PCA), the vectorized tensor feature is transformed to the ultimate vector feature representation, making TMDP robust to the noise by PCA's noise-filtering role. The algorithm is then compared to other traditional vector-based feature selection methods such as LDA, LPP, PCA, DLA, GMSS, HMSS, etc. Results show that TMDP outperforms in each proposed comparison.

Then, in [88], the research team investigates the use of template matching for recognizing sports activities using one single accelerometer worn at the wrist. This work differs from the others because of its limited sensing hardware (a single accelerometer) and the final generalized application target in terms of subject, sensor, and measurement-axis. Relating to this last aspect, the aim is to evaluate the ability of a template-matching classification algorithm to generalize on a population of overweight subjects. The system is evaluated by processing data collected in a gym environment, and results are compared with four popular classifiers: Decision Trees, Naive Bayesian, Logistic Regression, and Artificial Neural Network. The low accuracy obtained with the best template-matching metric is imputed to the lower accuracy in classifying cross trainer and rowing activities.

## 2.2.3 Wearable Devices

Among HAR systems, those exploiting wearable wireless devices are the most challenging. Differently from fixed sensors, a wearable sensor faces some constraints: 1) size and weight must be so to make the device less invasive as possible; 2) battery lifetime must be long enough to not force the user to frequent recharges; 3) the accuracy must be comparable with other fixed devices.

It is clear that each point is constraining each other (e.g. a lower size may lead to a lower battery capacity and so to less lifetime) so an application-related trade-off has to be found after context evaluation.

Referring to point 2), several research activities have been done to demonstrate how that goal can be reached by acting on both the hardware and firmware side.

#### **Optimization for Battery Lifetime**

One of the main key points of a wearable device is the battery lifetime. To provide the right user experience, a wearable device must be able to work continuously as much as possible, so as to avoid the user charging (and not using) it too frequently. The first and easier solution is to increase the battery capacity. This is a good practice until the object becomes too big and heavy to carry. Excluding the battery capacity increase, some ways to achieve the result have been tested by several research groups.

In [89], a Wi-Fi wearable system suitable for ambient assisted living is shown. The challenge here is to build a Wi-Fi-based system (as to be able to exploit the existing home wireless and internet user infrastructure) capable to provide ambient assisted living features. This work focuses on the energy management of the Wi-Fi module, a communication system that lacks strong energy policies and born to support higher-speed transfer rates and wider area coverage when compared to systems typically employed in home environments (e.g. Zigbee, Bluetooth, etc.). Thanks to a deep study of both hardware and firmware techniques, the group obtains a prototype wearable device able to match the operational lifetime of sensors relying on the aforementioned energy-aware communications systems.

A different approach has been used in [90], where the energy saving is achieved

by dynamically set the sampling rate of the sensible element (an accelerometer) to reduce the transmitted packets over time. By evaluating the motion magnitude of the sensor, the algorithm is able to set a high sample rate if the sensor is moving or a low sample rate if it is steady. The lower sample rate configuration is defined as guaranteeing a minimum and predefined activity recognition accuracy. It is clear that this operating mode brings a trade-off between accuracy and energy saving, with the proposed method shown to have an overall energy saving of 45.9% when compared with the same device continuously streaming at the maximum sampling frequency (12 Hz). The observed accuracy loss in the activity recognition is 0.41%.

Another dynamic power solution has been identified in [91], this time on smart wearable systems used in infants' sleep monitoring. The technique is based on a Transmission Power Control (TPC) mechanism that changes its characteristics according to the scenario of operation. It uses Inertial Measurements Unit (IMU) sensors to determine the position of the infant and, based on that, predicts the current state of the channel by evaluating RSSI signals. In the end, a comparison is done considering other state-of-the-art TPC algorithms and different infant positions. When compared with the same device at full transmission power (0 dBm), the proposed TPC mechanism reaches a maximum energy saving of up to 47% depending on the infant position.

In [92], the Authors introduce NEON, a wearable fall detector based on a low power MCU (Texas Instruments MSP480), two accelerometers, a barometer, an RF transceiver, and a single 3V, 1Ah coin cell battery. In addition, the paper reports a study on the classification features to be selected to build an energy-efficient fall detection wearable device. The group analyses a large set of data coming from a single accelerometer collecting data at 50 Hz and related to 10 young healthy volunteers, each one performing predefined actions to be classified as falls or non-falls. Those data have been then processed to find the best energy-efficient features (in terms of computational power required by the MCU in the calculation) to be used in the binary decision tree algorithm of choice. After the features selection, the system has been assessed and proved to have a power saving of 75.3% when using four out of ten of the most used features for this task in literature. The reduced number of features

affected the system with an error rate of 7.1% in the recognition accuracy.

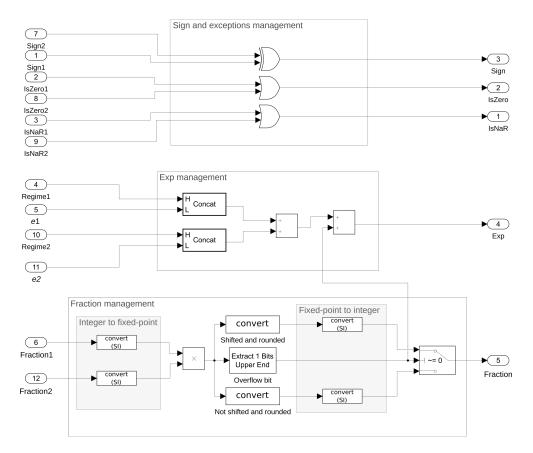

The same NEON wearable device was exploited in [93] to propose further energysaving techniques, which are somehow similar to [91]. In addition, to describe the right low-power hardware, the system here also benefits of particular accelerometers configuration: one accelerometer serves as the "static" sensor (ACCsm, sampling in low-power at 6 Hz) and the other one is used as the "dynamic" sensor (ACCfd, sampling in the power-hungry 50 Hz frequency). If the system is in a stationary mode, only ACCsm is on and, once ACCsm senses an intense motion, ACCfd is also turned on to catch a possible fall. This technique, combined with a computation-efficient features extraction to be used in the SVM classifier, led to a system with an estimated battery lifetime of 1,125 days.