## UNIVERSITA' DEGLI STUDI DI PARMA

DOTTORATO DI RICERCA IN

SCIENZA E TECNOLOGIA DEI MATERIALI

Ciclo XXX

# ELECTRICAL CHARACTERIZATION OF LOW TEMPERATURE PULSED-ELECTRON-DEPOSITED CU(IN,GA)SE<sub>2</sub> SOLAR CELLS

<u>Coordinator:</u> Chiar.mo Prof. Enrico Dalcanale

<u>Tutore:</u> Dott. Enos Gombia Dott. Massimo Mazzer

Dottorando: Aldo Kingma

Anni 2014-2017

## Abbreviations and symbols

| A                     | Ideality factor                                               | $\Delta C_{\rm N1/N2}$ | Capacitance step related to N1/N2 defect contributions (in AS)   |

|-----------------------|---------------------------------------------------------------|------------------------|------------------------------------------------------------------|

| A <sub>j</sub>        | Area of the junction in a solar cell                          | c-Si                   | Crystalline Silicon                                              |

| AC                    | Alternating Current                                           | C-V                    | Capacitance-Voltage profiling                                    |

| ALT                   | Accelerated Lifetime Test                                     | d                      | Layer thickness (of ODC layer)                                   |

| Al-ZnO                | Aluminium doped Zinc-Oxide                                    |                        |                                                                  |

| AM1.5                 | Air Mass 1.5                                                  | DC                     | Direct Current                                                   |

| AR                    | Anti-reflection                                               | DH                     | Damp Heat                                                        |

| AS                    | Admittance Spectroscopy                                       | E                      | Energy                                                           |

| BIPV                  | Building Integrated Photovoltaics                             | $\vec{E}$              | Electric field vector                                            |

| С                     | Capacitance                                                   | E <sub>A</sub>         | Acceptor energy level inside the bandgap                         |

| C                     | Capacitance                                                   | E <sub>a</sub>         | Activation energy of (dominant) recombination mechanism          |

| С                     | Speed of light in vacuum,                                     | E <sub>C</sub>         | Lowest energy in the conduction band (see CBE)                   |

|                       | (3×10 <sup>8</sup> m/s)                                       | F                      |                                                                  |

| <i>C</i> <sub>0</sub> | Highest observed capacitance value, at low frequency and high | E <sub>D</sub>         | Donor energy level inside the<br>bandgap                         |

|                       | temperature (in AS)                                           | E <sub>d</sub>         | Defect energy level inside the bandgap                           |

| $C_{\infty}$          | Saturation value of the<br>capacitance, at high frequency and | E <sub>F</sub>         | Fermi-level                                                      |

|                       | low temperature (in AS)                                       |                        | Electron Fermi-level                                             |

| СВ                    | Conduction Band                                               | E <sub>F,N</sub>       |                                                                  |

| CBD                   | Chemical Bath Deposition                                      | E <sub>F,p</sub>       | Hole Fermi-level                                                 |

| CBE                   | Conduction Band Edge                                          | E <sub>G</sub>         | Bandgap energy of a<br>semiconductor                             |

| СВО                   | Conduction Band Offset                                        | E <sub>ph</sub>        | Photon energy                                                    |

| CIGS                  | Cu(In,Ga)Se <sub>2</sub>                                      | E <sub>T</sub>         | Energy inside the bandgap at                                     |

| CIS                   | CuInSe <sub>2</sub>                                           |                        | which a trap level is centred                                    |

| CGI                   | Cu to Ga and In ratio (Cu/(Ga+In))<br>in composition of CIGS  | eqe<br>E <sub>v</sub>  | External Quantum Efficiency<br>Lowest energy in the valence band |

| CGS                   | CuGaSe <sub>2</sub>                                           | -v                     | (see VBE)                                                        |

|                       |                                                               |                        |                                                                  |

| f               | Frequency                                                                                              | MPP              | Maximum Power Point                                                                             |  |

|-----------------|--------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------|--|

| f(E, T)         | Fermi-Dirac distribution                                                                               | Ν                | Carrier density                                                                                 |  |

| FF              | Fill Factor                                                                                            | n                | Free electron density                                                                           |  |

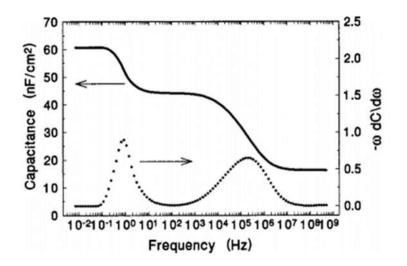

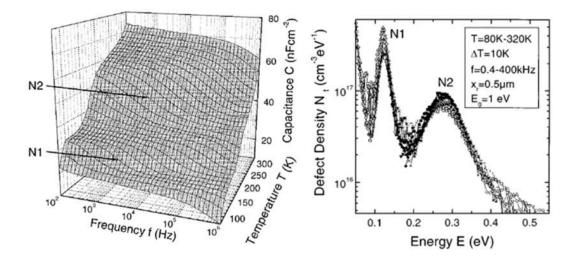

| FTO             | Fluoride-dope Tin Oxide                                                                                | N1               | Often reported step observed in                                                                 |  |

| GGI             | Relative Ga to Ga and In content<br>(Ga/(Ga+In)) in CIGS composition                                   |                  | capacitance at high frequency and low temperature (in AS)                                       |  |

| h               | Planck's constant,                                                                                     | N2               | Often reported step observed in<br>capacitance at low frequency and<br>room temperature (in AS) |  |

|                 | 6.62607004 × 10 <sup>-34</sup> m <sup>2</sup> kg/s                                                     | N                |                                                                                                 |  |

| HRW             | High Resistive Window layer                                                                            | N <sub>A</sub>   | Acceptor density                                                                                |  |

| Ι               | Light intensity                                                                                        | N <sub>D</sub>   | Donor density                                                                                   |  |

| ITO             | Indium Tin Oxide                                                                                       | n <sub>i</sub>   | Free electron density in intrinsic semiconductor                                                |  |

| IV<br>IV T      | Current-Voltage characteristics                                                                        | n <sub>N</sub>   | Free electron density in an N-<br>doped semiconductor                                           |  |

| IV-T            | temperature-dependent current-<br>voltage measurements                                                 | ODC              | Ordered Defect Compound                                                                         |  |

| i-ZnO           | Intrinsic Zinc-Oxide                                                                                   | OVC              | Ordered Vacancy Compound                                                                        |  |

| J <sub>o</sub>  | Saturation current density                                                                             | р                | Free hole density in intrinsic semiconductor                                                    |  |

| J <sub>D</sub>  | Diode current (in the equivalent circuit for a solar cell)                                             | PED              | Pulsed Electron Deposition                                                                      |  |

| J <sub>L</sub>  | Current density in a solar cell due<br>to illumination (in the equivalent<br>circuit for a solar cell) | p <sub>i</sub>   | Free hole concentration in intrinsic semiconductor                                              |  |

| J <sub>MP</sub> | Current density at the MPP                                                                             | P <sub>In</sub>  | Power incident on a solar cell                                                                  |  |

| J <sub>sc</sub> | Short circuit current density                                                                          | P <sub>Max</sub> | Power output from solar cell at MPP (i.e., maximum power                                        |  |

| k               | Crystal momentum                                                                                       |                  | output)                                                                                         |  |

| k <sub>B</sub>  | Boltzmann constant,                                                                                    | p <sub>p</sub>   | Free hole density on P-doped                                                                    |  |

|                 | $1.38 \times 10^{-23} \text{ m}^2 \text{ kg s}^{-2} \text{ K}^{-1}$                                    |                  | semiconductor                                                                                   |  |

| LRW             | Low Resistance Window layer                                                                            | poly-Si          | Polycrystalline Silicon                                                                         |  |

| LTPED           | Low Temperature Pulsed Electron<br>Deposition                                                          | PV               | Photovoltaic or Photovoltaics                                                                   |  |

| m               | Electron effective mass                                                                                | Q                | Static charge                                                                                   |  |

| m <sub>e</sub>  |                                                                                                        | q                | Elementary charge                                                                               |  |

| m <sub>h</sub>  | Hole effective mass                                                                                    |                  | (1.60217662 × 10 <sup>-19</sup> C)                                                              |  |

|                 |                                                                                                        |                  |                                                                                                 |  |

| QE              | Quantum Efficiency                                      | V <sub>OC</sub>    | Open-circuit Voltage                                             |  |  |

|-----------------|---------------------------------------------------------|--------------------|------------------------------------------------------------------|--|--|

| QNR             | Quasi Neutral Region                                    | V <sub>OC</sub> -T | Temperature-dependent open-                                      |  |  |

| RF              | Radio-Frequency                                         |                    | circuit voltage measurements                                     |  |  |

| R <sub>S</sub>  | Series resistance                                       | < x >              | Apparent depletion layer width in<br>presence of defect response |  |  |

| R <sub>Sh</sub> | Shunt resistance                                        | x <sub>N</sub>     | N-side of the depletion region<br>inside a P-N junction          |  |  |

| SCR             | Space Charge Region (depletion region)                  | Хр                 | P-side of the depletion region                                   |  |  |

| SLG             | Soda Lime Glass                                         |                    | inside a P-N junction                                            |  |  |

| SRH             | Shockly-Read-Hall (refers to                            | α                  | absorption coefficient                                           |  |  |

|                 | recombination mechanism)                                | α-Si               | amorphous Silicon                                                |  |  |

| STC             | Standard Test Conditions                                | e                  | Dielectric constant                                              |  |  |

| sq              | 'Square' for expressing sheet<br>resistance (i.e. Ω/sq) | Φ                  | Photon flux (cm <sup>-2</sup> )                                  |  |  |

| Т               | Temperature                                             | $\Phi^p_B$         | Recombination barrier to holes at                                |  |  |

| тсо             | Transparent Conductive Oxide                            |                    | CdS/CIGS interface                                               |  |  |

|                 |                                                         | n                  | Conversion efficiency                                            |  |  |

| TFSC            | Thin Film Solar Cell                                    | η                  |                                                                  |  |  |

| W               | depletion layer width                                   | λ                  | Wavelength                                                       |  |  |

| Wp              | Maximum power from a solar cell                         | $\tau^{-1}$        | Emission/capture rate of traps                                   |  |  |

|                 | under STC conditions                                    | $\tau_E^{-1}$      | Emission rate of traps                                           |  |  |

| V               | Externally applied bias                                 | μ(Τ)               | Chemical potential of electrons in                               |  |  |

| VB              | Valence Band                                            |                    | a semiconductor                                                  |  |  |

| VBE             | Valence Band Edge (see $\mathrm{E}_{\mathrm{V}}$ )      | μ-Si               | Microscrystalline Silicon                                        |  |  |

| V <sub>bi</sub> | Built-in potential                                      | σ                  | Conductivity                                                     |  |  |

| VBO             | Valence Band Offset                                     | ω                  | Angular frequency ( $2\pi f$ )                                   |  |  |

| V <sub>MP</sub> | Voltage across solar cell at the<br>Maximum Power Point |                    |                                                                  |  |  |

## <u>Abstract</u>

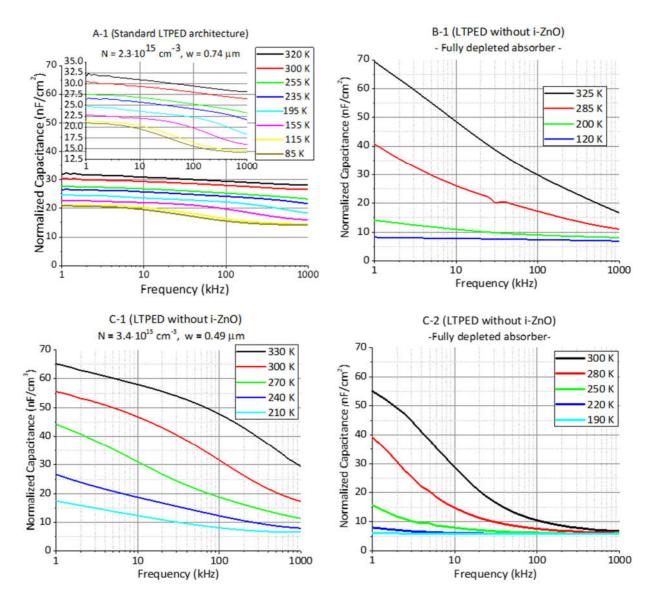

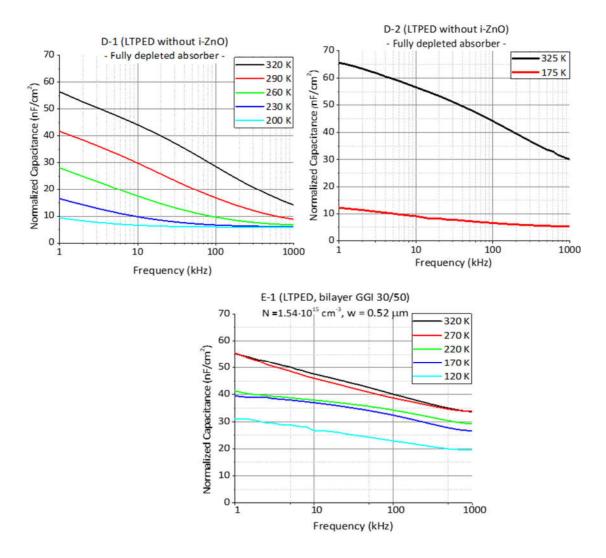

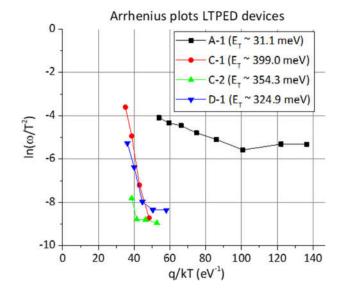

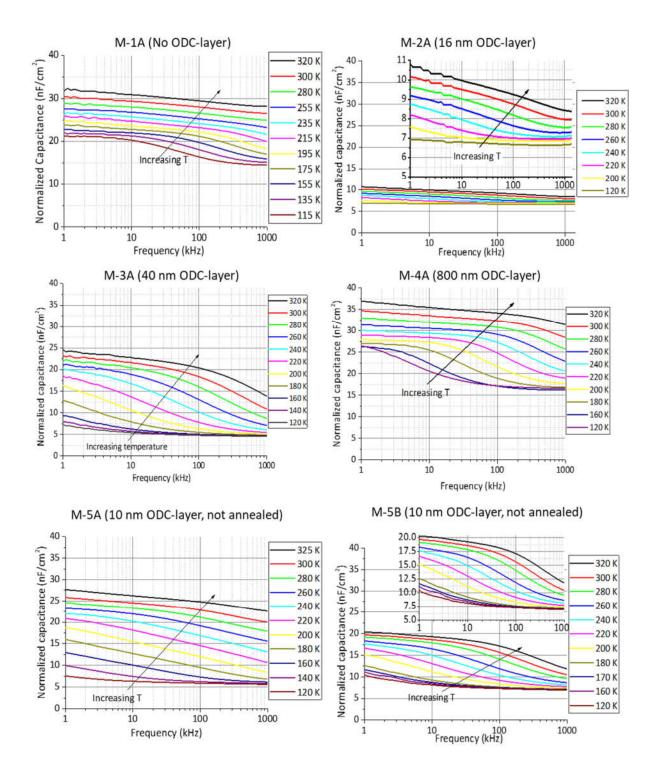

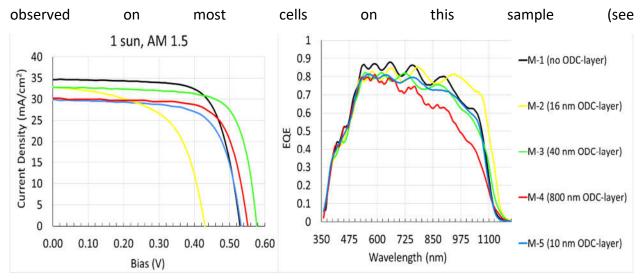

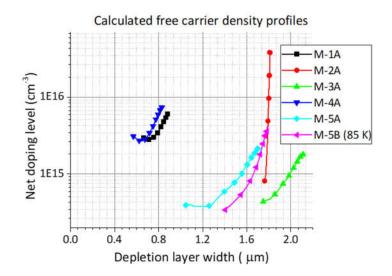

Thin Film Solar Cells (TFSC's) with Cu(In<sub>1-x</sub>,Ga<sub>x</sub>)Se<sub>2</sub> (CIGS)-absorber deposited by means of the novel Low Temperature Pulsed Electron Deposition (LTPED) technique developed at IMEM-CNR [1] were investigated with Admittance Spectroscopy (AS), Capacitance-Voltage profiling (*C-V*), temperature-dependent current voltage measurements (IV-T) and temperature dependent open-circuit voltage measurements (V<sub>oc</sub>-T) to obtain information about doping densities, defect characteristics and recombination mechanisms. The novelty of the LTPED technique is the achievement of a single stage deposition at low substrate temperature (250°C as opposed to the >350°C used in other processes) by using a stoichiometric target in the Pulsed Electron Deposition (PED) technique. The characterizations performed during this thesis allowed a more detailed comparison of the behaviour of CIGS-based devices created using LTPED (LTPED devices) and CIGS-based devices produced using more conventional deposition techniques. A methodology was developed to minimize metastable effects often reported for CIGS-based devices [2] [3] [4] [5] from influencing the measurement results, and for each technique the most relevant frequency-, temperature- and bias- were determined.

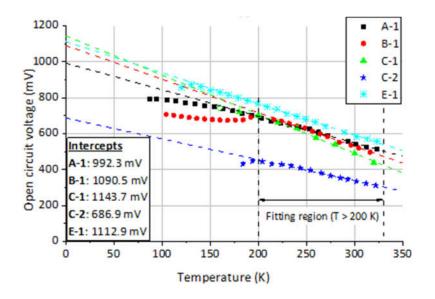

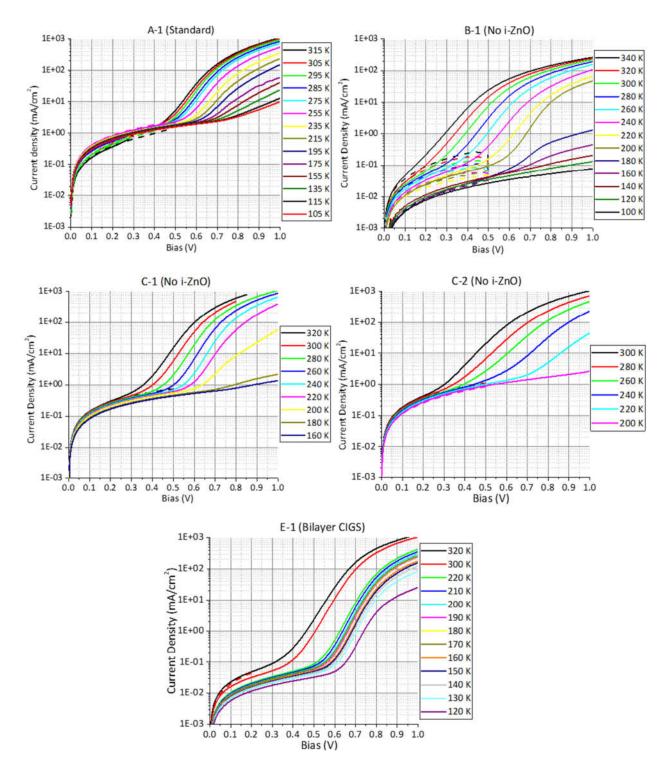

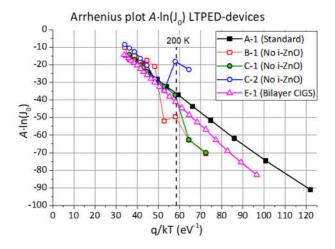

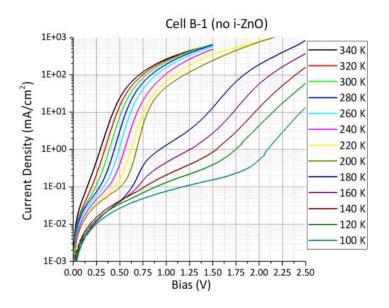

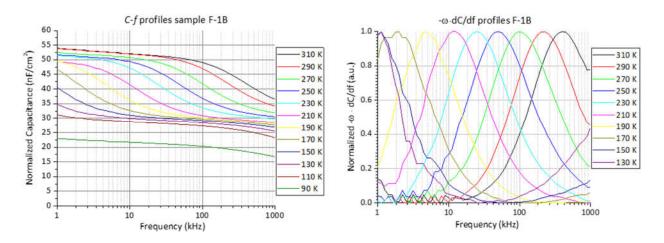

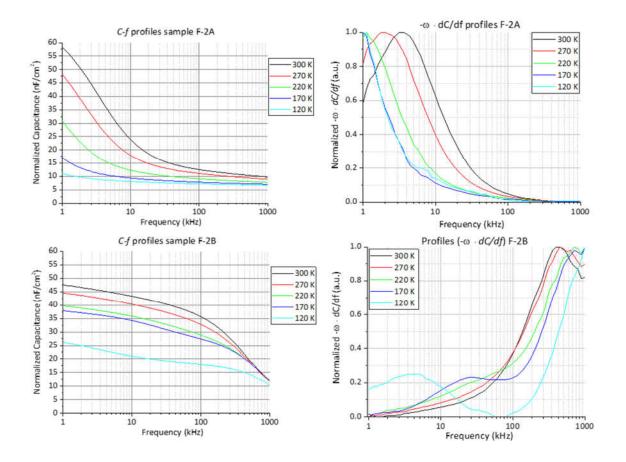

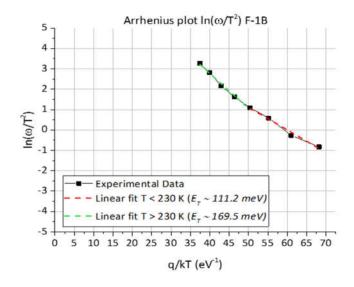

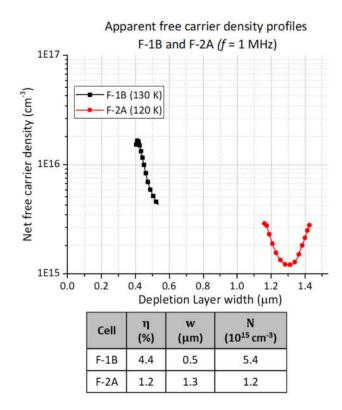

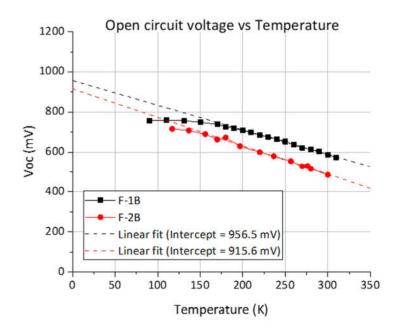

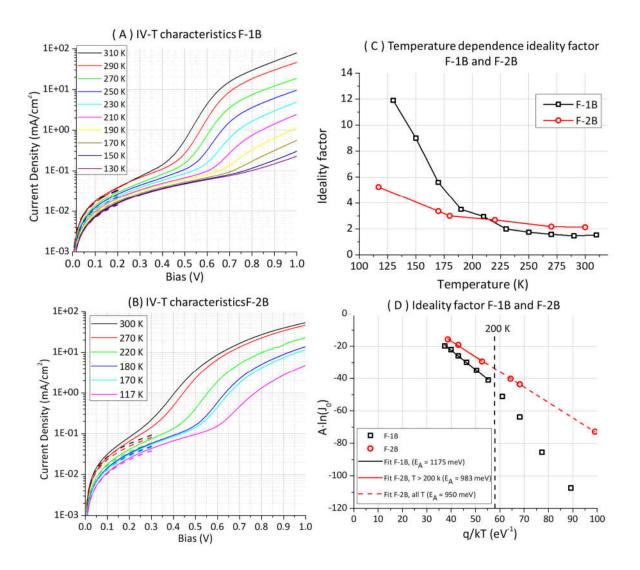

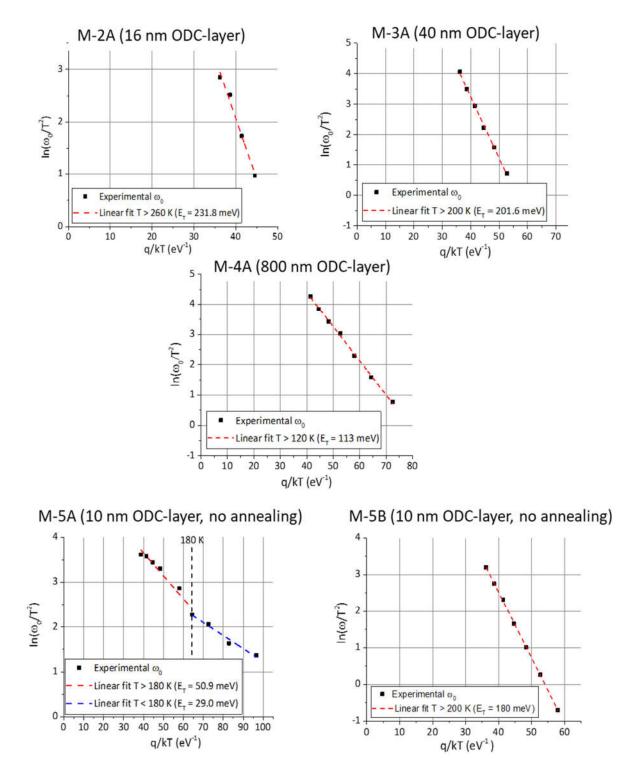

The best performing LTPED devices were found to have doping densities in the range of  $2\cdot 3\cdot 10^{15}$  cm<sup>-3</sup>, corresponding to depletion layer widths of w~0.5-0.75 µm [6]. Very often lower efficiencies could be attributed to insufficient doping. Although the AS-spectra varied significantly between investigated cells, in nearly each case a high defect density was observed and two separate steps in the capacitance similar to the 'N1' and 'N2' steps often reported in literature [7] [6] could be distinguished. For the step identified as the N1 step, the activation energy  $E_d$  of the trap-level was found to lie in the range of 40 meV  $\leq E_d \leq 250$  meV. From V<sub>oc</sub>-T and IV-T measurements the activation energy  $E_a$  of the dominant recombination mechanism in the temperature range 200 K  $\leq T \leq 350$  K was found to lie close to the absorber bandgap  $E_G$  (1000-1200 meV) for nearly all cells, suggesting Shockly-Read-Hall (SRH) recombination in the bulk of the absorber layer. For T < 200 K a lower activation energy was found, most likely indicating increased interface recombination or tunnelling enhanced interface recombination. For a small number of low efficiency cells ( $\eta < 10\%$ ) values for  $E_a < E_G$  were found for T > 200 K, indicating alternative

recombination paths such as interface recombination limited the efficiency also at normal operating temperatures.

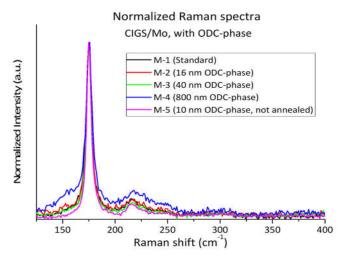

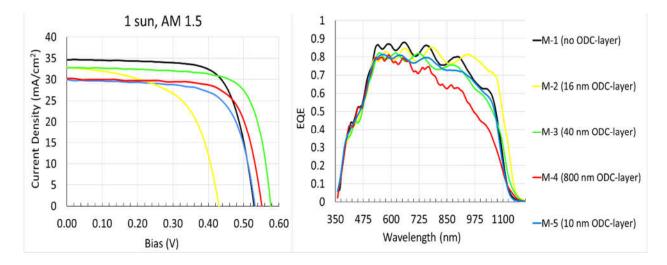

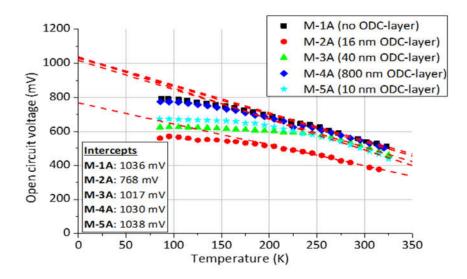

To test the feasibility of creating a homojunction device rather than the presumed P-N heterojunction between CdS and ClGS in standard devices, attempts were performed to deposit a layer of Ordered Defect Compound (ODC) phase of ClGS directly onto the surface of the P-type ClGS absorber using LTPED. Comparison of samples with expected ODC-layer thicknesses of d = 0, 10, 16, 40 and 800 nm only showed a significant loss in performance in the sample with the 800 nm ODC-layer, and an increase in the  $R_S$  and  $R_{Sh}$  values in the dark with increasing ODC-layer thickness. The increased  $R_S$  and  $R_{Sh}$  values in the dark were found to reduce to similar values as those observed on devices without ODC-layer upon illumination. These effects were attributed to a high photoconductivity in the ODC-layer due to a high concentration of defects, as also proposed in [8]. In this picture, the variations in the  $R_S$  values might be explained as a barrier for forward current being formed by the resistive ODC-layer in the dark, which reduces upon illumination as the conductivity of the ODC-layer covering shunting paths in the ClGS absorber, leading to reduced shunting in the dark. Under illumination, the increased conductivity of the ODC-layer would then explain the large reduction in  $R_{Sh}$ .

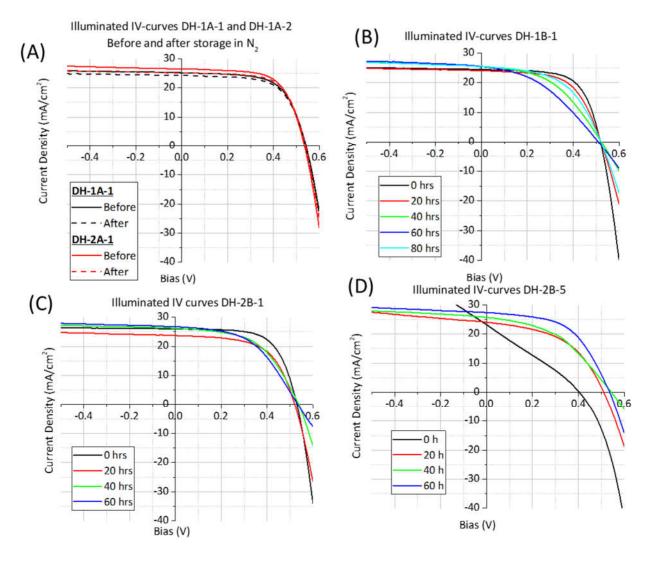

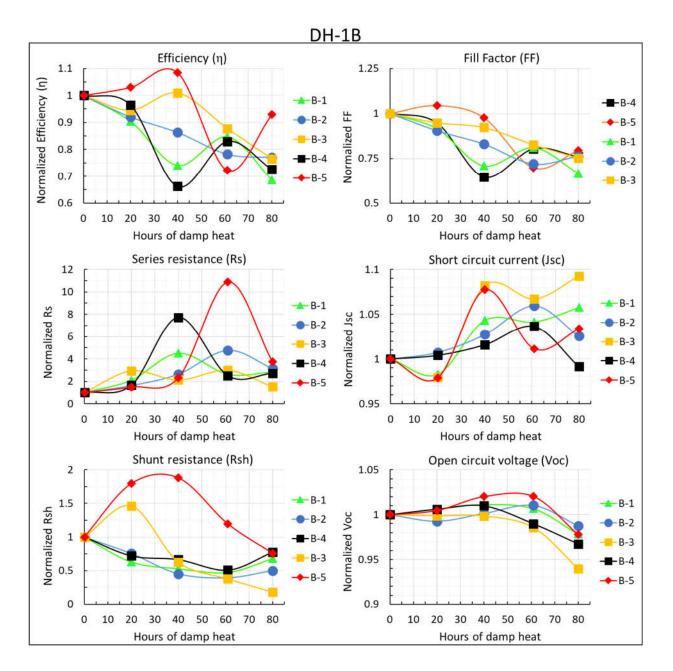

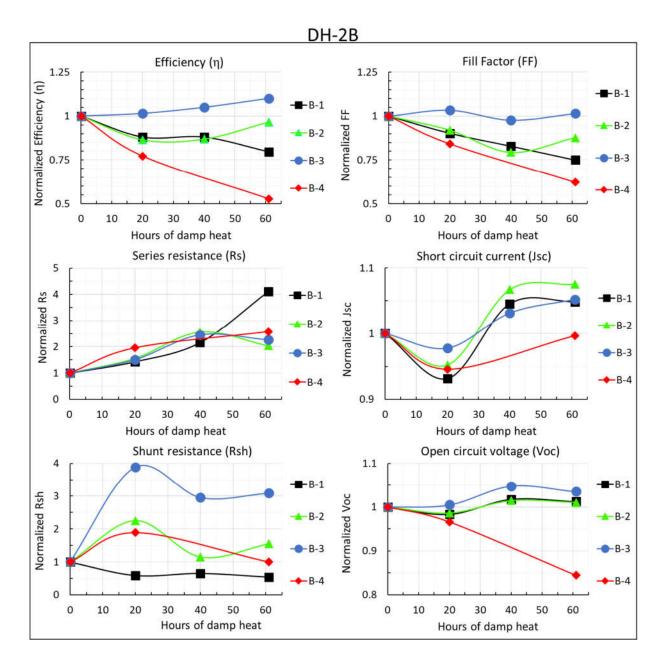

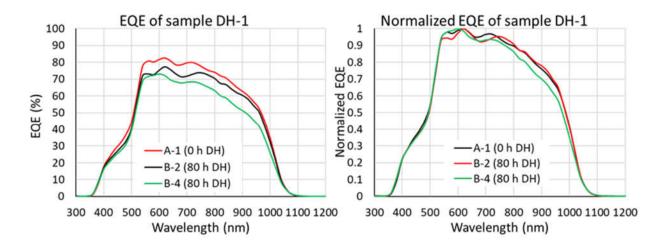

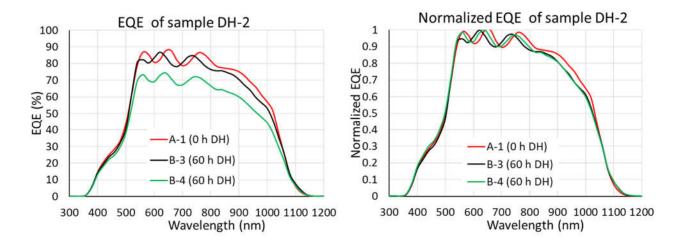

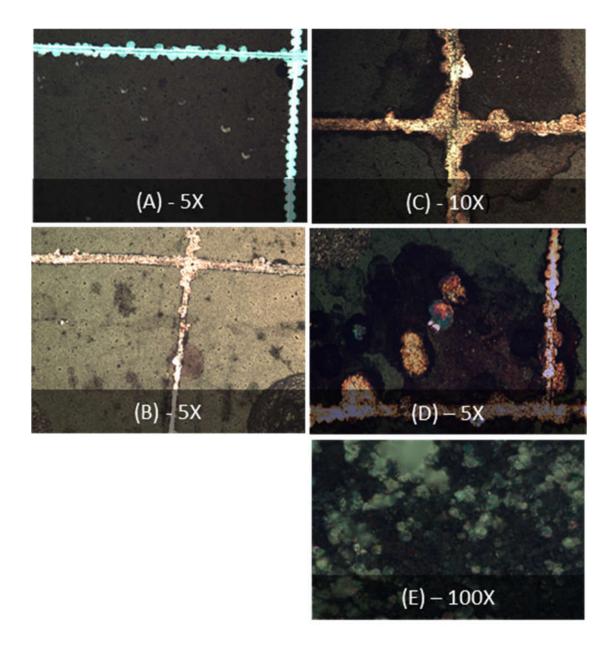

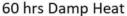

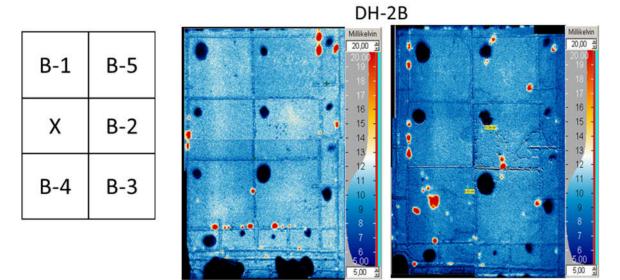

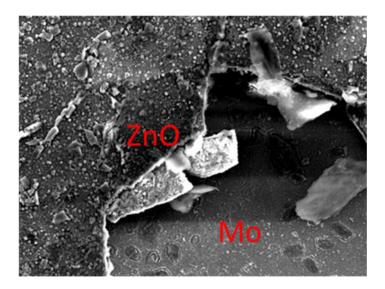

Accelerated lifetime tests (ALT's) in damp heat (DH, 85% relative humidity and 85°C) were performed on two LTPED devices with Ga/(Ga+In) ratio (GGI) of 0.375 and 0.3 for 60 and 80 hours respectively. As often reported in literature [9] [10] [11] [10] [12] the clearest effect of DH treatment was the degradation of the Mo and ZnO layers causing an increase in R<sub>S</sub>. Corrosion and oxidation of the Mo might also explain the observed losses in EQE at longer wavelengths ( $\lambda > 750$  nm) as discoloration of the Mo surface might cause a reduction in the amount of light reflected back into the CIGS absorber after reaching the back-contact. The generally observed decrease in R<sub>Sh</sub> was attributed to degradation and gradual disappearance of the absorber layer resulting in short-circuits between TCO and Mo back-contact. The observed disappearance of CIGS and formation of 'craters' in the absorber layer is expected to be a problem more relevant

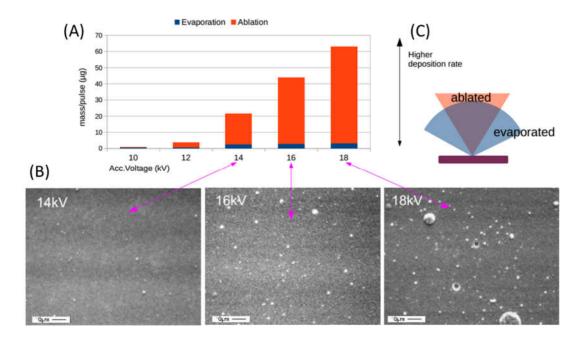

in LTPED devices, since in depositions by LTPED larger particulates/debris are known to be incorporated into the bulk of the CIGS film, which can eventually cause partial detachment [1].

In separate experiments the relevance of Na doping for formation of an ohmic contact in LTPED devices and the metastability and photoconductivity in CdS layers were investigated. Comparison of Mo/CIGS/Au and Mo/NaF/CIGS/Au samples strongly suggested that NaF can indeed allow a reduction of a back-contact barrier at the CIGS/Mo contact at temperatures for which no MoSe<sub>2</sub> is expected to form [13]. The underlying mechanism is thought to be formation of a thin, highly doped P<sup>+</sup>-layer at the CIGS/Mo interface allowing tunnelling of charge carriers. However, significant non-uniformity of was observed in this effect in the investigated samples. Measurements performed on a  $\sim$ 1 µm layer of CdS showed occurrence of photoconductivity with slow transients. This suggested a significant concentration of deep defects in the CdS buffer layers used in LTPED devices, which could have an important role in the metastability observed in LTPED devices.

# Table of Contents

| Absorber layer: Cu(In <sub>1-x</sub> Ga <sub>x</sub> )Se <sub>2</sub> (CIGS)            |

|-----------------------------------------------------------------------------------------|

| Buffer layer: Cadmium Sulfide (CdS)40                                                   |

| Window layer: Zinc-Oxide (i-ZnO) and Aluminum doped Zinc-Oxide (Al-ZnO)                 |

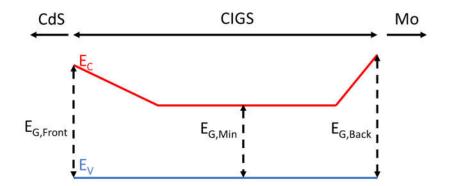

| Energy band diagram                                                                     |

| 2.2 Typical device behaviour and anomalies                                              |

| 2.2.1 Record and baseline devices                                                       |

| 2.2.2 Anomalies of CIGS-based devices                                                   |

| 2.3 CIGS material properties                                                            |

| 2.3.1 Phases and compositions                                                           |

| 2.3.2 Intrinsic defects                                                                 |

| 2.3.3 Extrinsic dopants                                                                 |

| 2.4 Deposition of CIGS absorber layers55                                                |

| 3 Electrical characterization techniques                                                |

| 3.1 Theoretical background                                                              |

| 3.1.1 Capacitive investigation techniques (AS and <i>C-V</i> )                          |

| 3.1.2 Temperature dependent current-voltage techniques (IV-T and V <sub>OC</sub> -T) 68 |

| 3.2 Experimental setup and methodology73                                                |

| 3.2.1 Temperature regulation74                                                          |

| 3.2.2 AS and <i>C</i> - <i>V</i> setups and approach77                                  |

| 3.2.3 IV-T and V <sub>OC</sub> -T setups and approach78                                 |

| 4 Standard CIGS by LTPED79                                                              |

| Introduction                                                                            |

| 4.1 Low Temperature Pulsed Electron Deposition                                          |

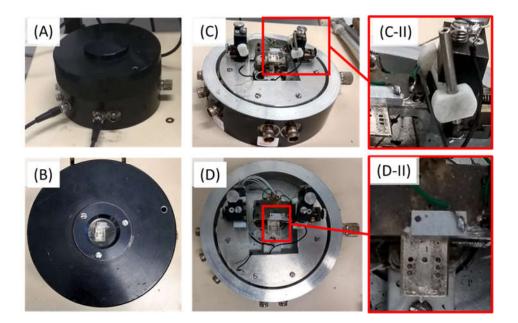

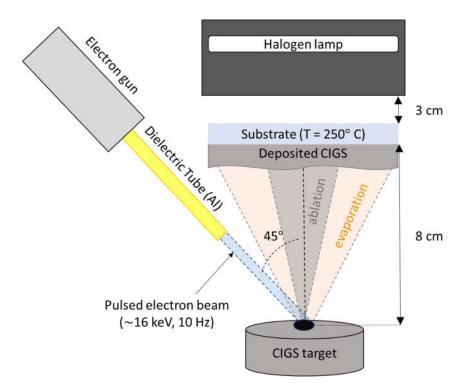

|   |     | 4.1. | 1      | Experimental setup: Pulsed Electron Deposition              | 79             |

|---|-----|------|--------|-------------------------------------------------------------|----------------|

|   |     | 4.1. | 2      | Target preparation                                          | 33             |

|   | 4.2 | 2    | LTP    | ED device architecture and preparation                      | 34             |

|   |     | Sub  | stra   | te: commercial SLG/Mo/Si <sub>3</sub> N <sub>4</sub>        | 35             |

|   |     | NaF  | Pre    | cursor and CIGS absorber                                    | 35             |

|   |     | Buff | fer la | ayer: CdS                                                   | 36             |

|   |     | Win  | Idov   | v layer (i-ZnO and Al-ZnO) and metallic front contacts (Al) | 37             |

|   |     | Rec  | ord    | efficiencies and current goals                              | 38             |

|   | 4.3 | 3    | Тур    | ical electrical characteristics of LTPED devices            | 39             |

|   |     | 4.3. | 1      | Standard performance                                        | <del>)</del> 0 |

|   |     | 4.3. | 2      | Defect response and charge carrier density                  | <del>9</del> 6 |

|   |     | 4.3. | 3      | Recombination mechanisms10                                  | )6             |

|   |     | 4.3. | 4      | Summary and conclusions1                                    | 12             |

| 5 |     | ODO  | C-ph   | ase CIGS in LTPED-devices1                                  | 14             |

|   | Int | trod | ucti   | on1                                                         | 14             |

|   | 5.: | 1    | Ехр    | erimental approach: LTPED deposition of ODC-phase CIGS      | 15             |

|   | 5.2 | 2    | Con    | ntribution of ODC-layer to measured capacitance1            | 18             |

|   | 5.3 | 3    | Sam    | nples CIGS/FTO1                                             | 19             |

|   | 5.4 | 4    | Sam    | nples CIGS/MO: variation of ODC-phase thickness1            | 32             |

|   | 5.  | 5    | Sun    | nmary and conclusions14                                     | 16             |

| 6 |     | Dan  | np h   | eat and degradation14                                       | 18             |

|   | Int | trod | ucti   | on14                                                        | 18             |

|   | 6.: | 1    | Acc    | elerated Lifetime Tests (ALT) and Damp Heat treatment14     | 48             |

| 6.2     | Experimental approach                 | 150 |

|---------|---------------------------------------|-----|

| 6.3     | Results: degradation of LTPED devices | 151 |

| 6.4     | Summary and conclusion                | 161 |

| Conclus | ions and perspectives                 | 163 |

| Append  | lix A. Measurement techniques         | 168 |

| Stand   | dard current-voltage (IV)             | 168 |

| Exter   | nal Quantum Efficiency (EQE)          | 168 |

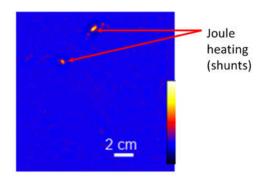

| Lock-   | In Thermography                       | 170 |

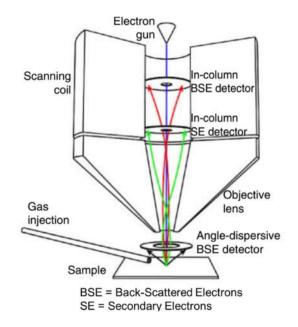

| Scanr   | ning Electron Microscopy (SEM)        | 171 |

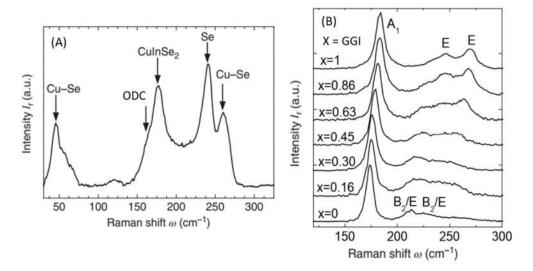

| Rama    | an spectroscopy                       | 173 |

| Optic   | al microscopy                         | 174 |

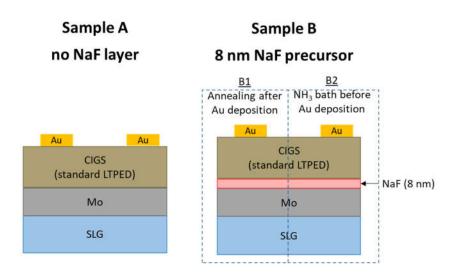

| Append  | lix B. CIGS/Mo interface              | 174 |

| Expe    | rimental approach and results         | 175 |

| Conc    | lusions                               | 180 |

| Append  | lix C. CdS photoconductivity          | 182 |

| Expe    | rimental approach                     |     |

| Resul   | lts                                   |     |

| Conc    | lusions                               | 185 |

| Acknow  | /ledgements                           | 186 |

| Referen | ices                                  | 189 |

## **Introduction**

### **GLOBAL ENERGY TRANSITION**

The negative effects of the use of fossil fuels, such as air pollution and accelerated global warming, as well as the finite reserve of these fuels available on earth, have caused a rise in awareness that alternative and cleaner sources of energy are essential. The energy consumption has grown exponentially the past century, and can be expected to continue increasing at similar or higher rate the coming century.

The sharp increase in the global energy demand during the past century has caused an almost equal increase in fossil fuel consumption and hence an increase in emission of waste gases. The negative impacts on the environment due to these exhaust fumes have by now become clearly noticeable from the dangerous levels of air pollution in many industrialized areas and an accelerated rate of global warming. These effects in combination with the recent increase in oil and gas prices have caused a growing incentive for an energy transition during the past few decades. This is reflected in the increase of investments done worldwide in both research and installation of renewable energy sources, which have caused over a doubling of installed capacity during the past 10 years.

As also clear from Table 1Error! Not a valid bookmark self-reference., the relative contribution from solar power to the total production of renewable energy is still small. However, this renewable energy resource has also been growing extremely fast. In 2012 the total capacity of solar power connected to the grid was estimated as slightly below 100 GW, while in 2016 it was estimated as 306.5 GW of which 76.6 GW was installed in 2016 alone [14]. This enormous growth was triggered in part by the aforementioned increase in investments in renewable energy research, but mostly by a steep drop in the costs of conventional solar cells at the start of the century. The lower cos of solar energy has allowed 'grid-parity' to be reached in many countries, meaning energy can be obtained from solar power at equal or lower cost as from the general grid. The current record for lowest sales-price of solar power is 2.4 US cents/kWh [14].

Table 1 Comparison of the contributions of solar power to the total power supply and total power capacity installed, as reported in [14]. Installed capacities refer to that installed at the end of 2007 and 2016.

|                  | Total capacity installed (GW) |            | Total produced power (TWh) |            |       |        |

|------------------|-------------------------------|------------|----------------------------|------------|-------|--------|

|                  | 2007                          | 2016       | Growth                     | 2007       | 2015  | Growth |

|                  |                               |            |                            |            |       |        |

|                  |                               |            | (%)                        |            |       | (%)    |

|                  |                               |            |                            |            |       |        |

| Renewable energy | 994.1                         | 2,011.3    | 102.3                      | 3,531      | 5,537 | 56.8   |

| Solar power      | 9.26                          | 295.9      | 3095                       | 8.2        | 253.6 | 2992   |

| Of which PV      | 95%                           | <u>99%</u> |                            | <u>92%</u> | 96%   |        |

|                  |                               |            |                            |            |       |        |

In light of the high energy density of the solar radiation falling onto the earth's surface, solar power is a promising technology that can allow to achieve the necessary transition to renewable energies.

#### **INNOVATIONS IN PHOTOVOLTAICS**

The most common and probably most convenient method of harvesting solar power for modern day purposes is by using solar cells. Solar cells are based on the application of semiconductor materials that allow direct conversion of incident photons into electricity through the photovoltaic effect (see sections 1.1 of Chapter 0).

#### From conventional to Thin Film Solar Cells (TFSC's)

The first commercial solar cells were based on Silicon (Si). This was an obvious material choice considering the suitable properties of Si for application in solar cells (see section 1.2 of Chapter 0), its' abundance on earth and the large amount of experience that was already available regarding its processing for electronics. The earliest Si-based solar cells used pure monocrystalline Si (c-Si) wafers, which require expensive and complicated production processes [15]. Later, also polycrystalline (poly) Si, microcrystalline ( $\mu$ ) Si and amorphous ( $\alpha$ ) Si were developed, offering a less expensive alternative but also with lower efficiency. In 2016 still 94% of the produced solar cells were based on Si, of which 70% of the solar cells was based on poly-,

$\mu$ - or  $\alpha$ -Si category [16]. Most likely, also in the future Si will continue to dominate the market of photovoltaics.

The other ~6% of market share in photovoltaics is taken up by a more recent technology referred to as 'Thin Film Solar Cells' or TFSC's. The thickness of the absorbing layer ('absorber layer') in TFSC's is in the order of ~1  $\mu$ m, while in typical c-Si solar cells a thickness in the order of ~100  $\mu$ m is required for sufficient light absorption. The lower thickness of TFSC's is achieved by application of alternative materials with higher absorption efficiency than Si (also see section 1.2 of Chapter 0) and leads to significantly lower material costs. In addition, thinner solar cells can be made flexible or semi-transparent, allowing more innovative application in e.g. Building Integrated Photovoltaics (BIPV) where solar cells are incorporated into various parts of normal building architecture. This type of application which allows covering more of the available surface area with solar cell technology will become increasingly important as the contribution of solar power will continue to grow. Flexible TFSC's are also promising for 'roll-to-roll' processing which can lead to higher throughput [17].

The TFSC's that are currently available on the market are mainly based on  $\alpha$ -Si, Cadmium Telluride (CdTe) and Cu(In,Ga)Se<sub>2</sub> (CIGS). Until now, TFSC's based on CdTe and CIGS have reached the highest efficiencies among this type of solar cell, with records of up to 15.7% on commercial modules. They were also found to have relatively high durability and stable in performance for such a novel technology (also see Chapter 2 and Chapter 5) [18]. For this thesis, CIGS-based devices were studied.

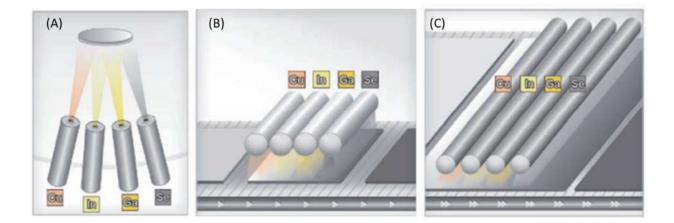

#### Developments in Cu(In,Ga)Se2 deposition approach

Obtaining the suitable phase of CIGS for PV applications is quite challenging (see section 2.3.1 of Chapter 2). In most conventional deposition techniques this requires multiple processing steps, high substrate temperatures ( $\geq 400^{\circ}$ C) and possibly toxic gases such as H<sub>2</sub>Se (see section 2.4 of Chapter 2). The complexity of typical deposition techniques makes them difficult to scale up and obtain higher throughput. The high substrate temperature limits the range of substrate materials that can be used for the final devices.

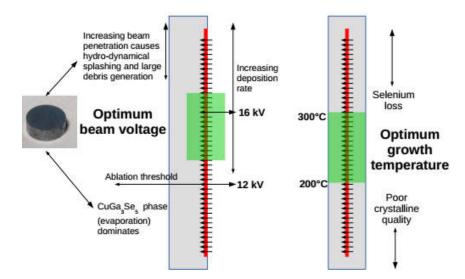

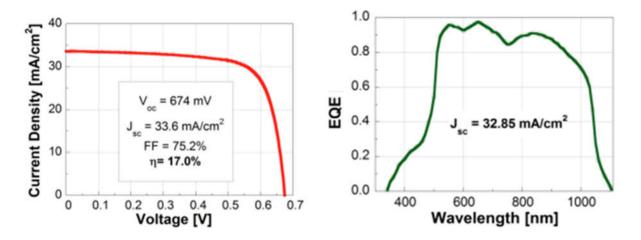

At IMEM-CNR an approach to CIGS thin film deposition using Pulsed Electron beam Deposition (PED) was developed, in which a single stoichiometric CIGS target and a substrate temperature of only ~250°C are used. With this 'Low Temperature Pulsed Electron Deposition' (LTPED) technique, good quality CIGS films and functional PV devices with record efficiencies of 17% have been obtained [19]. The devices investigated during this thesis were deposited with this novel LTPED technique, and will be referred to as "LTPED-devices" in the following.

#### AIM AND SCOPE OF THIS THESIS

The aim of this thesis was to determine the electrical properties of LTPED devices, with a strong focus on aspects related to defect response, recombination mechanisms and doping and net free carrier densities. Defects (i.e. imperfections in the crystal lattice) are usually present in high concentrations in CIGS thin films and play an important role in determining the behaviour of CIGSbased TFSC's [20]. The different defects and their role in device behaviour will be treated in more detail in section 2.3.2. By studying the abovementioned properties indications of the limiting factors in the efficiency in LTPED-devices were obtained, and the doping levels of the devices were determined to verify the effectiveness of the preparation approach. A prerequisite for obtaining the results presented in this thesis was identifying the most suitable approach for performing the different characterization techniques, taking into account influences from metastability and transients in device operation (see 2.2.2.2). Hence, the first part of this thesis was focused on determining the best methodology to obtaining reproducible results from the electrical characterization of the LTPED devices. The most important results from this thesis were obtained using current-voltage (IV-T), open-circuit voltage versus temperature (V<sub>OC</sub>-T), admittance spectroscopy (AS) and capacitance-voltage (C-V) measurements. Further background regarding the different measurement techniques and the established methodology are discussed in more detail in Chapter 3. The established methodology was applied to LTPEDdevices with a number of different architectures.

A smaller part of this thesis concerned investigations of the photoconductivity and metastabilities in the buffer layer material (CdS), the influence of an NaF precursor layer on the formation of an ohmic contact at the interface between the CIGS layer and the back-contact (Mo), and accelerated lifetime tests (ALT's) performed on LTPED devices. Although the investigations regarding the CdS and Mo/CIGSIn particular the investigations regarding the photoconductivity in CdS and the contact at the CIGS/Mo interface were relatively small and inconclusive, they were useful in the interpretation of the results from the main investigations.

### THESIS OUTLINE

Chapters 1, 2 and 3 of this thesis contain some background theory. In Chapter 0 some basics regarding semiconductors and their application in PV devices are treated. In Chapter 2 a more detailed background is given regarding CIGS-based TFSC's and their typical behaviour. In Chapter 3 the basic theory regarding the IV-T,  $V_{OC}$ -T, *C-V* and AS characterization techniques is presented the applied methodology is described.

The main results of this thesis are presented in the Chapters 4 to 6. Chapter 4 contains both an introduction to the LTPED deposition technique and LTPED device preparation, and the results obtained for devices with standard architecture. In Chapter 5 the results obtained from the investigation of LTPED-devices in which an attempt was made to deposit an additional layer of an 'Ordered Defect Compound' or ODC-phase material are presented. Chapter 6 contains the results from Accelerated Lifetime Tests (ALT's) on a small number of LTPED devices, and some preliminary conclusions that could be obtained regarding limiting factors in the lifetime of this type of device. After a presentation of the results, the conclusions and perspectives are given. The appendices contain a list of the different measurement techniques that were used (Appendix A), the investigations regarding the formation of an ohmic contact at the CIGS/Mo interface (Appendix B) and the investigations regarding photoconductivity in the CdS buffer layer (Appendix C).

## 1 Background of solar cells

## INTRODUCTION

This chapter contains some important theory about solar cells and their operation and introduces the terminology used to describe solar cell performance. In section 1.1 the photovoltaic effect, the fundamental functionality of a solar cell, is described in some detail. In section 1.2 the most important requirements that need to be met to achieve efficient photovoltaic conversion of solar energy are discussed, and the standard approach to analysing and describing the performance of solar cells is explained.

## 1.1 <u>The photovoltaic effect</u>

The photovoltaic effect refers to formation of an electric field and current following the excitation of charge carriers (electrons and holes) by photons incident on a material or device. In most solar cells this is achieved by implementing a P-N junction diode, a device formed from two layers of semiconductor material. Before arriving at the photovoltaic effect in P-N junctions in section 1.1.2, some relevant theory and terminology regarding semiconductor properties is introduced in section 1.1.1. A more complete and detailed description of semiconductor properties is given in, for example, references [21] and [22]

#### 1.1.1 Intrinsic semiconductors and generation/recombination

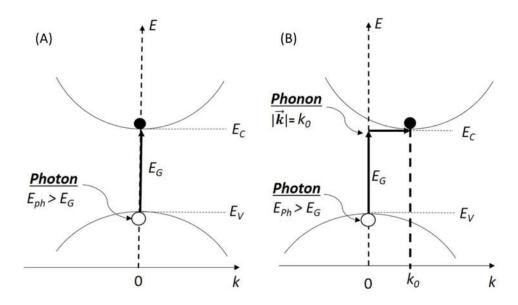

Semiconductors are materials with a low intrinsic conductivity at room temperature, which can be changed by adding impurities (i.e. 'doping' the material). The low intrinsic conductivity is due to restrictions in the energies E and momenta **k** that electrons can attain inside the material. These restrictions follow from Bloch's theorem, which states that the dispersion relation  $E(\mathbf{k})$ between allowed energies and momenta needs to have periodicity in **k** corresponding to the spatial periodicity of the crystal lattice. The allowed combinations  $E(\mathbf{k})$  are usually visualized using a band-diagram, an example of which is shown in Figure 1. In the lowest energy configuration of a semiconductor the electrons will fill up the lowest available distinct states. This results in a range of energies that would be occupied even at 0 K, which the Valence Band (VB) with highest energy (the Valence Band Edge or VBE) at  $E_V$ . The allowed states that remain unoccupied in this configuration define the Conduction Band (CB) with lowest energy  $E_C$  (the Conduction Band Edge or CBE). The VBE and CBE are separated by an energy gap or bandgap  $E_G = E_C - E_V$  where no allowed electron states exist. Electrons can then be excited from the VBE to the CBE under excitations with energy satisfying  $E > E_G$ .

Figure 1 Examples of band-diagrams illustrating the difference between the absorption processes in a direct (A) and indirect (B) bandgap semiconductor. Open circles indicate holes (empty electron states) and filled circles indicate electrons.

Once an electron reaches the CB it can give rise to conduction by moving between the large number of unoccupied energy states. The corresponding equation of motion is similar to that of a free particle if an 'effective mass'  $m_e$  is introduced to take into account the forces due to the potential of the atoms forming the crystal lattice. Hence, an electron in the CB is often referred to as 'free charge carrier' or 'free carrier'. Empty electron states in the VB also give rise to electron transport by allowing electrons in the VB to move from occupied to unoccupied states. This type of conduction is most easily described by considering the empty electron state as a virtual positive charge carrier (hole) which also acts as free particle with effective mass  $m_h$  (much higher than  $m_e$  for electrons). In an intrinsic semiconductor, every free electron in the CB will

correspond to a free hole in the VB, so that the concentration of free electrons n will always equal the concentration of free holes p.

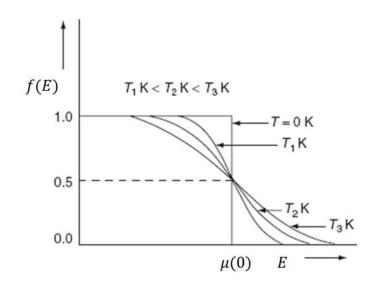

The probability of occupation of an electron state depends on the energy of the state E and the temperature of the system T, as given by the Fermi-Dirac distribution (Equation 1.1)

$$f(E,T) = \frac{1}{1 + \exp\left(\frac{E - \mu(T)}{kT}\right)}$$

1.1

Here,  $\mu(T)$  is the chemical potential for electrons in the material. Note that this probability distribution doesn't take into account whether the state is actually allowed in the semiconductor crystal. For the distribution of allowed states a different density of states function is used. At 0 K, f(E) forms a step function which gradually smooths out at higher temperatures, as shown in Figure 2.

Figure 2 Fermi-Dirac distribution plotted for 0 K and three temperatures  $T\,$  > 0 K [23]

The energy  $E = \mu(T)$  is referred to as the Fermi-level  $E_F$ . From the given expression for f(E) it follows that  $f(\mu(T)) = \frac{1}{2'}$ , so that if an allowed electron state would exist at the Fermi-level it would have equal probability of being occupied and unoccupied.

For an intrinsic semiconductor, the condition n = p results in a symmetric distribution around the centre of the bandgap, so that  $E_F \sim \frac{E_G}{2}$  at all temperatures. For doped semiconductors the introduction of additional electron states leads to a shift in the probability distribution (and therefore  $E_F$ ) toward either the VB band or CB. Hence, from the position of  $E_F$  a useful indication of the conductivity properties of a semiconductor is obtained.

The creation of free carriers in a semiconductor can occur through thermal, optical or electrical excitations and is referred to as free carrier *generation*. In stationary conditions free carrier generation is balanced by carrier *recombination*, the opposite process in which electrons from the CB drop to the VB and 'recombine' with holes. Different possible routes for carrier recombination exist in a semiconductor, as will be discussed specifically for Cu(In,Ga)Se<sub>2</sub>-based devices in Chapter 4. Of course, for photovoltaics the process of free carrier generation by absorption of incident photons (i.e. band-to-band absorption) is particularly important. This process is illustrated in Figure 1 for a direct bandgap (where VBE and CBE occur at the same value of **k**) and an indirect bandgap (where VBE and CBE occur at different values of **k**). For a direct bandgap, a photon with energy  $E_{ph} \ge E_G$  is sufficient to excite an electron to the CB. For an indirect bandgap an additional momentum  $\mathbf{k_0}$  needs to be provided, which requires a phonon (lattice vibration) since the momentum of photons is usually negligible. This makes band-to-band absorption much less probable for indirect bandgap semiconductors than for direct bandgap semiconductors.

The amount of band-to-band absorption in a semiconductor follows the Lambert-Beer law, where upon incidence of light at intensity  $I_0$  the amount of light remaining after passing through a thickness x of the semiconductor is given by

$$I = I_0 \exp(-\alpha x)$$

1.2

Here,  $\alpha$  is the absorption coefficient and has units of inverse length. It depends on the photon energy  $E_{ph}$  (and hence photon wavelength according to  $E_{ph} = \frac{hc}{\lambda}$ ) and the semiconductor bandgap  $E_{G}$ . The expression for  $\alpha$  is quite different for direct and indirect bandgap

semiconductors due to the different mechanisms involved. For a direct bandgap,  $\alpha$  the dependence of  $E_{ph}$  and  $E_G$  is given by:

$$\alpha \propto a \sqrt{E_{\rm ph} - E_{\rm G}}$$

1.3

Here a is a constant. For indirect semiconductors the dependence becomes quadratic:

$$\alpha \propto a \left( E_{\rm ph} - E_{\rm G} \right)^2$$

1.4

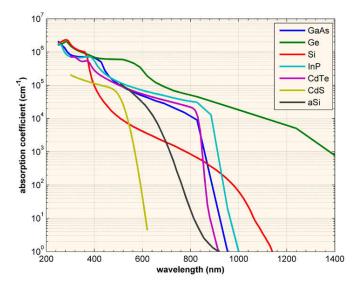

The absorption coefficients are shown as function of wavelength for a number of direct and indirect bandgap semiconductors in Figure 3. The much higher absorption coefficients of direct bandgap semiconductors indicates they require much less material to achieve the same amount of absorption, which makes them advantageous for photovoltaic applications.

Figure 3 Absorption coefficient as function of wavelengths for a number of semiconductors often used in photovoltaics: Si (red curve, indirect bandgap), Ge (green curve, both direct and indirect bandgap),  $\alpha$ -Si (black curve, large number of indirect bandgaps), and the direct bandgap semiconductors GaAs (dark blue curve), InP (light blue curve), CdTe (pink curve) and CdS (yellow curve) [24]

#### 1.1.2 Semiconductor doping and P-N junctions

The conductivity of a semiconductor can be changed from intrinsic to P-type (conduction via holes in the VB) or N-type (conduction via electrons in the CB) by appropriate doping. P-type

conductivity is achieved by introducing impurities that can take-up electrons from the VB (acceptor impurities) resulting in the formation of an acceptor energy level at  $E_A$ , with  $(E_A - E_V \le kT)$ . Introduction of the acceptor level at  $E_A$  close to the VB results in a higher occupation probability of states in the energy range  $E \le \frac{E_G}{2}$  than in the intrinsic case, so that  $E_F$  shifts towards the VB. Analogously, to achieve N-type conductivity impurities that can give-off electrons to the CB (donor impurities) are introduced, resulting in the formation of a donor energy level at  $E_D$  with ( $E_C - E_D \le kT$ ). In case of presence of a donor level, the increased probability of states in the energy range  $E > \frac{E_G}{2}$  causes a shift of  $E_F$  towards the CB.

Since  $(E_A - E_V) < kT$  and  $(E_C - E_D) < kT$ , nearly all impurities can be expected to be ionized at room temperature. For a P-type semiconductor with acceptor concentration N<sub>A</sub> the free hole concentration will be approximately given by  $p_P \approx N_A + n_i$ , with  $n_i$  the intrinsic carrier concentration. For a N-type semiconductor with donor concentration N<sub>D</sub> the free electron concentration will be approximately given by  $n_N \approx N_D + n_i$ . The more abundant free carriers are referred to as 'majority carriers' while those at lower concentration are referred to as 'minority carriers'. The minority carriers generated in a semiconductor will have a high probability of recombining due to the much higher concentration of majority carriers. The average time it takes for minority carriers to recombine is referred to as the minority carrier lifetime, with the expected distance the minority carriers can travel without recombining referred to as the minority carrier diffusion length. Usually electrons have a longer minority carrier lifetime/diffusion length than holes due to their lower effective mass, which is an important consideration in the design of the P-N junction, as discussed in section 1.2.

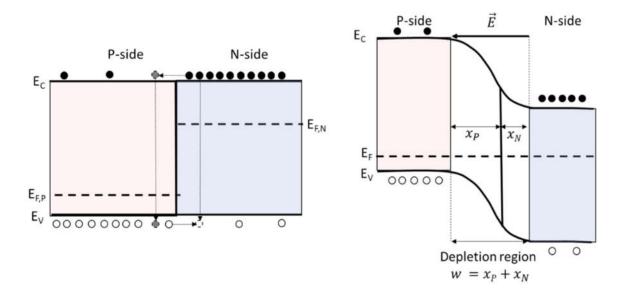

To establish a photovoltaic effect, majority and minority carriers need to be separated after their generation by incident photons. One common way to achieve this carrier separation is by using a combination of a N-type and P-type semiconductor in a P-N junction, as illustrated in Figure 4.

At formation of the interface between the N-type and P-type material, the large gradient in charge carrier concentrations on both sides gives rise to a diffusion current of electrons from N-side to P-side and holes from P-side to N-side, as illustrated in Figure 4. Electrons arriving at the

24 | Page

P-side become minority carriers and quickly recombine with majority carrier holes, leaving behind positively charged donors on the N-side and negatively charged acceptors on the P-side.

Figure 4 Band-diagram for a P-N junction near the interface before (left) and after (right) reaching equilibrium.  $E_{F,P}$  and  $E_{F,N}$  refer to the Fermi-level for electrons on the P-side and N-side of the junction respectively. Closed circles represent electrons, open circles represent holes.

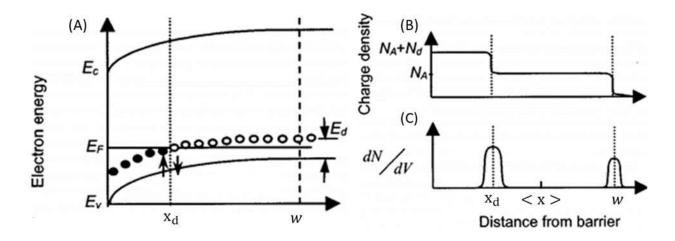

Thin layers with thicknesses  $x_N$  and  $x_P$  and only positively charged donors and negatively charged acceptors remain on the N-side and P-side respectively. The entire region with thickness  $w = x_N + x_P$  depleted of free carriers is referred to as the depletion region or 'space-charge region' (SCR).

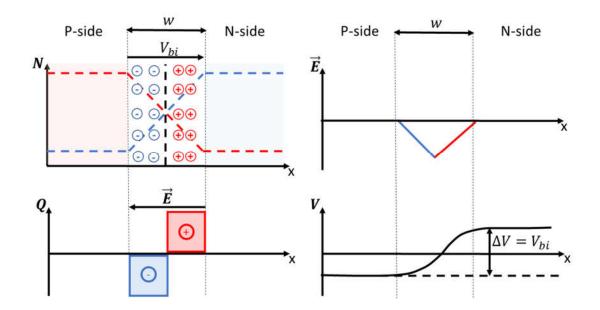

The fixed charge inside the SCR in an electric field directed from the N-side to the P-side, as also indicated in Figure 4. This electric field gives rise to a 'drift current' in opposite direction of the diffusion current, as electrons are swept from P- to N-side, and holes are swept from N- to P-side. Equilibrium is reached once the diffusion current and drift current balance each other. In Figure 5 the charge carrier densities, charge distribution, electric field and electric potential in a symmetric P-N junction are shown under equilibrium conditions.

The built-in potential  $V_{bi}$  across the junction at equilibrium can be expressed in terms of the intrinsic carrier concentration  $n_i$  and majority carrier concentrations on both sides of the junction (i.e.  $n_N$  and  $p_P$ )

$$V_{bi} = \frac{kT}{q} \cdot \left(\frac{n_N p_P}{n_i^2}\right) \approx \frac{kT}{q} \cdot \left(\frac{N_D N_A}{n_i^2}\right)$$

1.5

$$w = \sqrt{\left(\frac{2\epsilon(N_{A} + N_{D})}{q(N_{A}N_{D})}(V_{bi} - V)\right)}$$

1.6

Here,  $\epsilon$  is the dielectric constant of the semiconductor material. The external bias V is considered as positive or forward bias if it opposes V<sub>bi</sub> (with cathode at the P-side and the anode at the Nside) and as negative or reverse bias otherwise.

Figure 5 Schematic representation of the spatial distribution of charge carrier density N (red line = electrons, blueline = holes), static charge Q, electric field  $\vec{E}$  and electric potential V in a P-N junction with depletion layer width w in equilibrium.

At application of forward bias the depletion layer width will reduce as majority carriers are driven toward the depletion layer edges, and for high enough forward bias will become negligible. At application of reverse bias the depletion layer width will increase as majority carriers are pulled away from the depletion layer edges. The current will only slightly increase due to an increase in the drift current of minority carriers across the depletion layer. At high enough reverse bias the junction breaks down and the depletion layer disappears, causing a much faster increase in reverse current. In short, the P-N junction acts as a diode and allows current to pass relatively easily in forward direction, while resisting reverse current up to the break-down voltage.

The above-described internal electric field of a P-N junction allow it to be applied to obtain a photovoltaic effect. After band-to-band absorption of incident photons satisfying  $E_{\rm ph} > E_{\rm G}$ , minority carriers formed within a diffusion length distance from the edges of the depletion region will be swept to the other side of the junction by the internal electric field and become majority carriers. This leads to an increase in the majority carrier density on both sides of the junction after photo-excitation, and the build-up of an electric field and a current that can be driven into an external circuit.

### 1.2 SOLAR CELL DEVICES AND EFFICIENCY

Whereas the previous part of this chapter was concerned mainly with the fundamental theory regarding semiconductors and P-N junctions, the current part concerns the description of complete solar cells based on P-N junction diodes. In section 1.2.1 the most important requirements to obtain functioning solar cells for terrestrial purposes will be discussed, still mainly regarding the properties of the P-N junction. Section 1.2.2 is focused on the description of the behaviour of complete solar cells.

#### 1.2.1 From P-N junction to solar cell

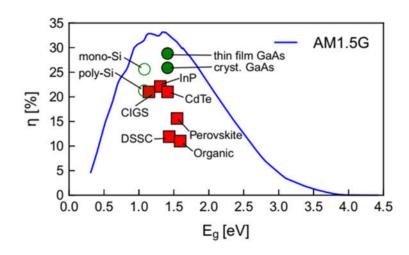

From section 1.1.2 above, it will be clear that the efficiency of photo-absorption, carrier separation and carrier collection in a solar cells are mainly determined by the quality of the P-N junction. As already described in section 1.1.1, the absorption coefficient and hence efficiency of absorption for a given wavelength or spectrum depends on the bandgap of the absorbing layer ('absorber layer') in the P-N junction. From consideration of the 'detailed balance limit' or 'Shockley and Queisser limit' [25] the maximum theoretical efficiency of 33.2% for conversion of

the solar spectrum was found to be achievable when using an absorber bandgap of 1.34 eV [26]. Hence, absorber layer materials used for solar cells typically have a bandgap in the range of ~1.0-1.5 eV as shown in Figure 6. Silicon (Si), by far the most common material in commercial solar cells, has a bandgap reasonably close to this value ( $E_{G,Si} \approx 1.17 \text{ eV}$ ) but has a relatively low absorption coefficient due to its indirect bandgap, as shown Figure 3. Alternative direct bandgap semiconductors are InP ( $E_G = 1.34 \text{ eV}$ ), GaAs ( $E_G = 1.42 \text{ eV}$ ), CdTe ( $E_G = 1.5 \text{ eV}$ ) and the Cu(In,Ga)Se<sub>2</sub> (~ 1.2 eV).

Figure 6 Plot of the theoretical limit in the photovoltaic conversion efficiency for a number of typical solar cell materials, as function of bandgap, calculated using the AM 1.5G standard reference spectrum for solar energy conversion on earth (see Figure 10) [26].

An important factor in limiting the charge carrier separation is the minority carrier diffusion length, since minority carriers need to be able to reach the depletion layer edge to be swept across the junction. Since electrons usually have a much larger minority carrier diffusion length than holes, most solar cells are designed to have the P-side of the junction as absorber layer where electrons form the minority carriers. This requires a much lower doping on the P-side than on the N-side so that  $w \approx x_P$ . The combination of materials used to form the P-N junction also has an important influence on the device efficiency. If the same semiconductor material is chosen for the N-side and P-side (a homojunction) the interface will be formed with the same crystal lattice on both sides, resulting in few interfacial defects and limited effects of interface recombination. When using two different semiconductors (forming a heterojunction) the lattice mismatch is likely to result in a much higher concentration of interfacial defects so that interface recombination will be more likely to limit collection efficiency. Also, a difference in bandgap will lead to a difference between the CBE and/or the VBE on both sides of the junction which translates into a Conduction Band offset (CBO) and/or Valence Band Offset (VBO). The presence of a CBO and VBO can form a barrier for photogenerated charge carriers.

At the same time, in a heterojunction the equal bandgap on both sides results in comparable absorption coefficients, while from the consideration of the lower minority diffusion length of holes absorption on the N-side is less desirable. Hence in this case a very thin layer of N-type material is more important to optimize carrier collection. An advantage of heterojunctions is that absorption in the N-type material can be prevented by using a high bandgap material that doesn't absorb in the spectrum relevant for absorption on the P-side.

Typical components present in solar cells in addition to the P-N junction and front-/back-contacts are window layers, buffer layers, and Anti-Reflection (AR) coatings. The presence of these additional materials is intended to increase efficiency of carrier transfer to front- and backcontacts, act as diffusion barriers, increasing the absorption (by e.g. limiting reflection losses or increasing reflection back into the absorber layer), reduce shunting effects and interface recombination [6]. A few examples of such components relevant for CIGS based devices are discussed in more detail in Chapter 2.

#### 1.2.2 Description and analysis of solar cell behaviour

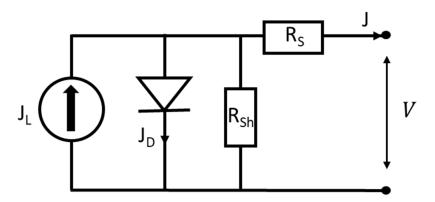

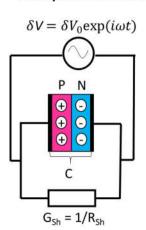

From the electrical behaviour of a P-N junction given in section 1.1.2, a single-junction solar cell can be modelled with the circuit shown in Figure 7. The diode with current density  $J_D$  (Equation 1.10) describes the behaviour of the P-N junction in the dark, and an ideal current source is used to model the current density  $J_L$  produced under illumination. The current density  $J_L$  depends on the intensity of incident light (with  $J_L = 0 \text{ mA/cm}^2$  in the dark) and is usually assumed to be independent of bias. The series resistance losses occurring throughout the various components of the a solar cell are modelled with a single ('lumped') series resistance  $R_S$ , and shunting losses are modelled with a single parallel or shunt resistance  $R_{Sh}$ . The total current density J through a solar cell can then be expressed as

$$J = J_D + \left(\frac{V - JR_S}{R_{Sh}}\right) - J_L$$

1.7

In Equation 1.8 the diode current  $J_D$  given by

$$J_{\rm D} = J_0 \left( \exp\left(\frac{q(V - JR_{\rm S})}{AkT}\right) - 1 \right)$$

1.8

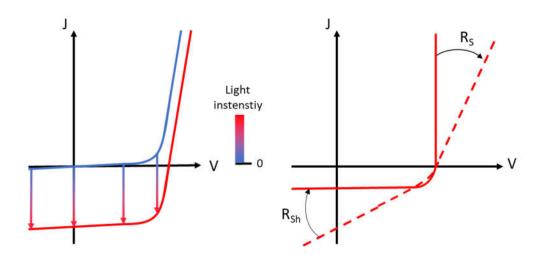

With A the ideality factor and J<sub>0</sub> the reverse saturation current density. An ideal solar cell without series resistance and shunting losses would have  $R_S = 0 \Omega \cdot cm^2$  and  $R_{Sh} = \infty \Omega \cdot cm^2$ . The effects of illumination,  $R_S$  and  $R_{Sh}$  are illustrated in Figure 8.

It should be noted that in actual devices care needs to be taken as to the range of bias, current and illumination intensities that is used for estimating values of  $R_S$  and  $R_{Sh}$ . These variations are caused by the different possible origins to both series and shunt resistance in actual devices. Also  $J_L$  typically has some bias-dependence [6] [27] [28] [29].

Figure 7 Model circuit of a simple solar cell

In the expression of the diode current  $J_D$  shown in Figure 7, the ideality factor A and reverse saturation current density  $J_0$  can also contain non-idealities in the diode behaviour, related to recombination mechanisms other than standard band-to-band recombination. In Chapter 3 a more detailed description will be given about how these parameters can be used to distinguish the different recombination mechanisms.

Figure 8 Current-voltage (IV) characteristics of a solar cell, with effects of illumination, series resistance and shunt resistance. Left: IV-curve in the dark (blue line) and under illumination (red curve), arrows indicate curve shift with increasing light intensity. Right: Illuminated IV-curve in the ideal case where  $R_{sh} = \infty$ ,  $R_s = 0$  (full-line) and for lower  $R_{sh}$  and higher  $R_{sh}$  (dashed line)

In the dark  $J_L = 0$  and the solar cell acts as a normal diode in presence of the resistances  $R_S$  and  $R_{Sh}$  in the circuit. Approximate values of  $R_S$  and  $R_{Sh}$  can be obtained from the dark IV characteristics from the inverse slope  $\left(\frac{dJ}{dV}\right)^{-1}$  at the bias regions where the respective resistances are expected to dominate. Typically,  $R_S$  is fitted at high forward biases where linear (Ohmic) behaviour is observed and  $R_{Sh}$  is derived from the region close to 0 V.

Under illumination, the shape of the IV-curve would ideally remain unchanged with respect to the dark curve, with the total current resulting from the sum of the dark current  $J_D$  and light generated current  $J_L$ , i.e.  $J = J_D + J_L$ . The power that can be produced by the solar cell is then given by the product of the current and voltage in the fourth quadrant if IV-characteristics are plotted as shown in Figure 8. Often, to obtain positive values of generated power the IV-curve is plotted as shown in Figure 9 with opposite sign of the current.

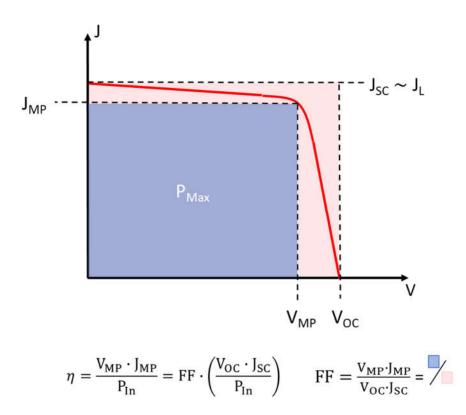

Figure 9 IV-curve of an illuminated solar cell (corresponding to the fourth quadrant of Figure 8 with indications of the open-circuit voltage  $V_{OC}$ , short-circuit current  $J_{SC}$ , and maximum power-point (MPP) with corresponding current  $J_{MP}$  and voltage  $V_{MP}$ . The expressions of the Fill Factor (FF) and solar cell efficiency ( $\eta$ ) are also shown, with  $P_{In}$  referring to the total power density of incident light.

Under illumination, the open-circuit voltage or  $V_{OC}$ , short-circuit current or  $J_{SC}$ , and the current density  $J_{MP}$  and voltage  $V_{MP}$  at the point at which maximum power is produced (MPP, with power density  $P_{Max}$ ) are important parameters to analyse the solar cell performance. The power  $P_{Max}$  measured under standard testing conditions (see below) is often expressed in the special unit 'Watt peak' (W<sub>P</sub>). By comparing  $V_{OC}$ ,  $J_{SC}$ ,  $V_{MP}$  and  $J_{MP}$  the Fill Factor (FF) can be calculated according to

$$FF = \frac{V_{MP} \cdot J_{MP}}{V_{OC} \cdot J_{SC}}$$

1.9

As shown in Figure 8, in the ideal case where  $R_S = 0$  and  $R_{Sh} = \infty$ , the illuminated IV-curve would be rectangular, with maximum power  $P_{Max}$  given by  $P_{Max} = V_{OC} \cdot I_{SC}$  ( $I_{SC}$  the short-circuit current) in which case FF = 100%. For a real device  $V_{MP} < V_{OC}$  and  $J_{MP} < J_{SC}$ , so that 0% < FF < 100% and the deviation of FF from 100% gives an indication of device quality. The most complete indication of solar cell performance is given by the conversion efficiency  $\eta$ , defined as the ratio of the maximum power  $P_{Max}$  and total power of incident photons  $P_{In}$ , as show in Figure 9:

$$\eta = \frac{(V_{MP} \cdot I_{MP})}{P_{In}} = FF \cdot \frac{(V_{OC} \cdot I_{SC})}{\Phi_{In} \cdot (area)}$$

1.10

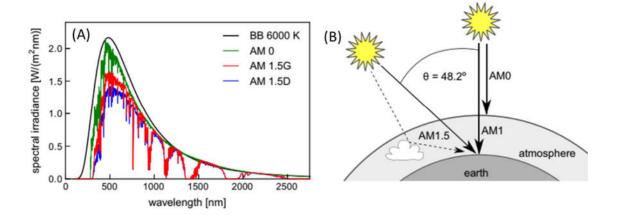

with  $\Phi_{In}$  the flux of incident power (W/m<sup>2</sup>). This expression indicates the sensitivity of the calculated efficiency to the illumination intensity and the actual area of the device used during measurement. The efficiency  $\eta$  also depends on the exact spectrum used for measurement since the conversion efficiency of a solar cell usually varies strongly with wavelength (this is referred to as the spectral response or 'Quantum Efficiency' (QE) as described in Appendix A. Measurement techniques. In consideration of the sensitivity of obtained results to measurement conditions, well-defined standard test conditions (STC) have been established. The current international standards are measurement at 25°C cell temperature and 1000 W/m<sup>2</sup> illumination with the 'air-mass' 1.5G (AM 1.5G) spectrum as shown in Figure 10. This spectrum is calculated assuming solar insolation at 41.8° above the horizon and taking into account absorption in the earth's atmosphere as well as diffuse light [26] [30]. In addition to measurement conditions, also the area that can be used for defining the efficiency follows strict guidelines [18].

Figure 10 A: Standard reference spectra used to model the solar spectrum outside of the earth's atmosphere (AM 0, green), at the earth's surface only considering light at direct incidence (AM 1.5D, blue), at the earth's surface considering both direct and diffuse light (AM 1.5G, red), radiation from a black-body at 6000 K (BB 6000 K, black line). B: Corresponding insolation assumed for each spectrum [26]. The AM 1.5G spectrum is considered as the standard in the remainder of this thesis.

33 | Page

# 2 Cu(In,Ga)Se<sub>2</sub>-based Thin Film Solar Cells

### INTRODUCTION

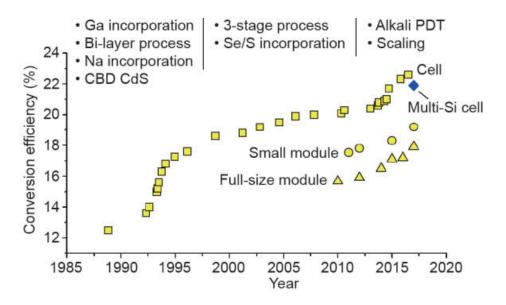

As treated in the introduction of this thesis, TFSC's are a relatively new technology in PV allowing a much smaller amount of material per unit of produced power (i.e. lower g/W<sub>P</sub> ratio) and a much wider range of applications than the more conventional Si-based devices. The wider range of applicability in e.g. Building Integrated Photovoltaics (BIPV) will become increasingly important considering the continued growth of the photovoltaic industry predicted for the next decade [14] [31] [32]. The quaternary semiconductor Cu(In,Ga)Se<sub>2</sub> (CIGS) is one of the most promising materials for TFSC's. It has a direct bandgap in the ideal energy range for solar energy conversion (1.04-1.68 eV), which results in an absorption coefficient of  $\sim 10^5$  cm<sup>-1</sup>, sufficient to absorb most incident light within a few µm's [33] [34]. The possibility to apply CIGS for PV was already realized in the early 1970's, when the first solar cells based on bulk single crystal CuInSe<sub>2</sub> (CIS) quickly reached conversion efficiencies exceeding 10% [35] [36]. The first thin-film devices followed shortly after and had initial efficiencies limited to ~5-6% [34], but owing to much research and development currently with CIGS the 20% efficiency record has been exceeded by various groups. In Figure 11 the progress in CIGS-based devices over the past 30 years is shown, with a number of sudden jumps in record efficiencies reflecting different discoveries in best preparation approach and architecture. Since the improvements don't show a sign of saturation yet it is expected that it will be possible to get closer to the theoretical limit of 30%.

On the laboratory scale, the verified efficiency record is currently at 22.6% [37] [18], which already exceeds the current record efficiency of 22.0% on the same scale devices based on multicrystalline Si. Transferring the high efficiencies of CIGS lab-scale cells to the modular scale has been a challenge due to issues in scaling up the most successful deposition techniques. Nevertheless, the 19.2% efficiency record currently reached on CIGS modules is only slightly lower than the 19.9% record for comparable poly-Si modules and proves CIGS technology can be highly competitive with conventional c-Si. Significant cost reduction in CIGS TFSC's are to be expected once further upscaling of production is achieved [38].

Figure 11 Graph showing the progress in conversion efficiency in laboratory scale (squares), small modules (circles) and full-size modules (triangles) CIGS-based TFSC's( [38]

### 2.1 <u>TYPICAL ARCHITECTURE FOR CIGS DEVICES</u>

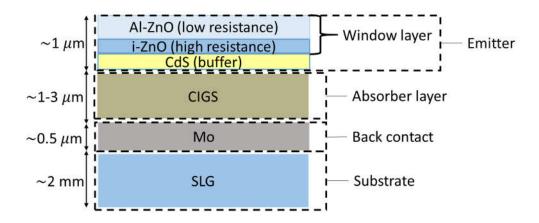

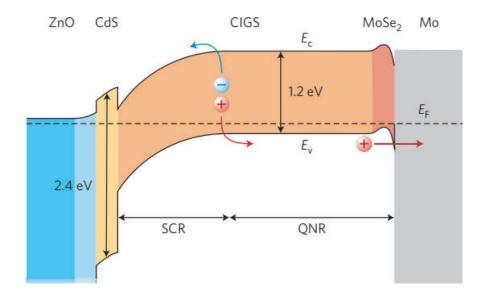

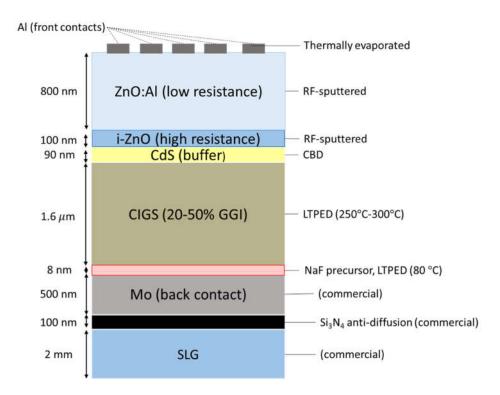

The conventional architecture for CIGS-based TFSC's shown in Figure 12 is based on a structure invented in 1987 at Arco Solar [6]: a Soda Lime Glass (SLG) substrate/Molybdenum (Mo) back contact/CIGS absorber layer/Cadmium Sulfide (CdS) buffer layer/thin intrinsic Zinc-Oxide (i-ZnO) high resistive window (HRW) layer/and an aluminium doped Zinc-Oxide (Al-ZnO) low resistance window (LRW) layer. In this architecture the P-N junction is formed close to the CIGS/CdS interface, by P-type CIGS and N-type CdS. Below, the function, deposition approach and material choice are explained and motivated for each layer. A more detailed description of the different deposition techniques for the CIGS absorber will follow in section 2.4.

Figure 12 Schematic representation of the conventional architecture used for CIGS-based TFSC's. The active part of the solar cell can be roughly divided into an emitter, absorber and back-contact, where the emitter consists of three layers: buffer-layer, high resistance window (HRW) layer and low resistance window (LRW) layer. The materials in this figure indicate the most common choice of materials for CIGS-based solar cells. In the text some alternatives are also described.

#### Substrate: Soda Lime Glass (SLG)

For thin film devices a substrate material is essential to offer mechanical support to the solar cell. The choice for SLG in CIGS-based devices was initially made in consideration of its wide availability, high durability to both the CIGS deposition conditions and normal operating conditions, and low cost. The later realization that sodium (Na) diffusion from the SLG substrate into the absorber layer during CIGS deposition leads to improved device performance made SLG the standard choice for substrates in CIGS-based devices [39, 40].

The numerous investigations performed during the past decade (see e.g. [6, 41] [42] [43] [44] [45] [46] [47, 48]) have increased the understanding of effects of Na-doping device performance, but at the same time much is still unclear or topic of discussion. Alternative approaches to supplying Na during the CIGS deposition [6, 49, 50, 41] have allowed SLG to become successfully substituted by other materials, mainly flexible metallic foils and polymers (polyimides). Metallic foils have the advantage of good resistance to temperatures well above the typical ~500 °C used for CIGS deposition, but the disadvantage of a relatively high diffusivity into the absorber layer. To prevent diffusion of metals into the CIGS absorber, a diffusion barrier (typically SiO<sub>2</sub> or Si<sub>3</sub>N<sub>4</sub>) can be placed between the metallic substrate and the Mo-back contact. The most suitable metals

for application as substrate for CIGS were found to be aluminium (AI), tin (Ti), nickel (Ni) alloys and stainless steel. Highest efficiencies, in the range of ~17.7-17.9%, have been reached on Ti substrates [51]. Polyimides have the advantage of being electrically insulating, allowing easier monolithic interconnection on large areas. They also don't contain impurities that could diffuse into the absorber layer. However, their inability to withstand temperatures above 500°C makes them unsuitable for application in the deposition approaches that until now allow reaching highest efficiencies. They also typically bend after deposition of the Mo-back contact, but this can be prevented by applying an insulating material on the back. The record efficiency reached on polyimides is currently at 20.4% [51, 52].

## Back-contact: Molybdenum (Mo)

The choice for Mo as back-contact in CIGS-based devices was made in consideration of its low contact resistance with the CIGS absorber, low diffusivity in the CIGS absorber, relatively low cost and high melting point (~2700 °C) [6, 53, 54]. A layer of ~300-1000 nm Mo is usually DC-sputtered directly onto the substrate at room temperature or deposited by electron beam evaporation at 300-400 °C [6]. To achieve good adhesion to the substrate and low resistivity at the Mo/CIGS a 'bilayer' structure is usually deposited: a first deposition at high pressure results in a layer with good adhesion to the substrate, a second deposition at lower pressure results in a layer with low resistivity [53].

The low resistivity at the CIGS/Mo interface has been correlated to formation of a MoSe<sub>2</sub> layer between CIGS and Mo at sufficiently high CIGS deposition temperatures [55] [56] [57]. The layered structure of MoSe<sub>2</sub> allows diffusion of Cu, In, Ga and Se from the absorber into the Mo, resulting in chemical intermixing at the Mo/CIGS interface and formation of either an Ohmic contact or a Schottky barrier [58]. The band-alignment between CIGS/MoSe<sub>2</sub>/Mo was found to limit electron recombination at the back contact, thus improving carrier collection [58]. The thickness of MoSe<sub>2</sub> layers formed during the CIGS deposition strongly depends on substrate temperature, Ga-grading and presence of Na in the absorber. While the highest observed thicknesses were ~100 nm, in samples without Na no MoSe<sub>2</sub> could be detected [6]. As will be discussed in Chapter 4, the low deposition temperature of 250°C used in LTPED doesn't allow formation of a MoSe<sub>2</sub> layer. Nevertheless, by supplying sufficient Na ohmic- or near-ohmic contacts have been obtained (see [54] and Appendix B).

# Absorber layer: Cu(In<sub>1-x</sub>Ga<sub>x</sub>)Se<sub>2</sub> (CIGS)

In addition to having a suitable bandgap for photovoltaic applications, CIS and CIGS have also shown a relatively high tolerance to compositional variations and good durability under normal operating conditions. This allows some tunability in important electrical properties such as bandgap and conductivity type without loss of absorber quality. This section contains a description of the most common compositions of CIGS used for photovoltaic applications, while a more general description of CIGS material properties follows in section 2.2.

The thickness of CIGS absorber layers usually lies in the range of 1-3  $\mu$ m. Although good light absorption would already be achieved using only 0.1-1  $\mu$ m of CIGS, a thickness of at least 1  $\mu$ m was found necessary to prevent openings occurring in the absorber layer which would form shunting paths [59]. Upper limits to the absorber layer follow from the maximum diffusion length of minority carriers, which should be able to reach the space charge region (SCR) from the bulk or neutral region of the absorber, and the diffusivity of dopants such as Na, which should be able to diffuse throughout the entire absorber to result in homogeneous doping.

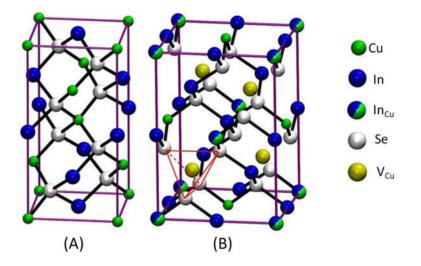

The most important variables in CIGS composition are the relative Cu-content, expressed as Cu/(In+Ga) or CGI, and the relative Ga-content, expressed as Ga/(Ga+In) or GGI. Variation of the CGI leads to variations in the phase and conductivity type of CIGS (see section 2.3). For good absorber layer quality, the bulk conductivity needs to be P-type which is achieved for CGI ~0.9, i.e. slightly Cu-poor compared to stoichiometric composition. Variation of the GGI leads to variations in the bandgap, where GGI = 0 corresponds to ~ 1.04 eV and GGI = 1 corresponds to ~1.68 eV. The best device efficiencies have been reached using GGI ~ 0.3, corresponding to a bandgap of ~ 1.2 eV. Although this is slightly lower than the theoretically ideal bandgap of ~1.4 eV for conversion of solar light as treated in Chapter 0 [25] [26], increasing the GGI beyond ~0.3

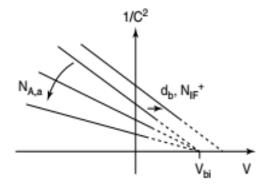

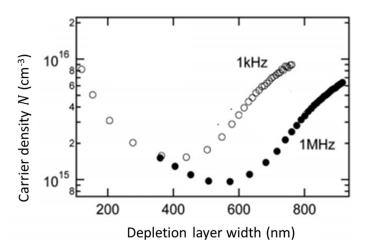

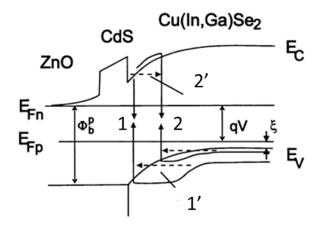

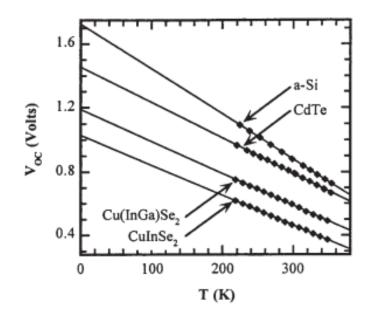

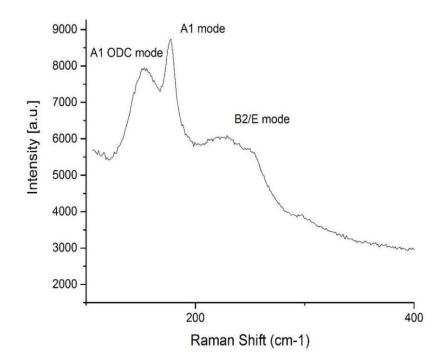

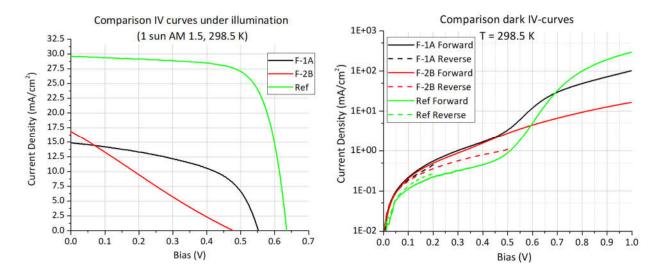

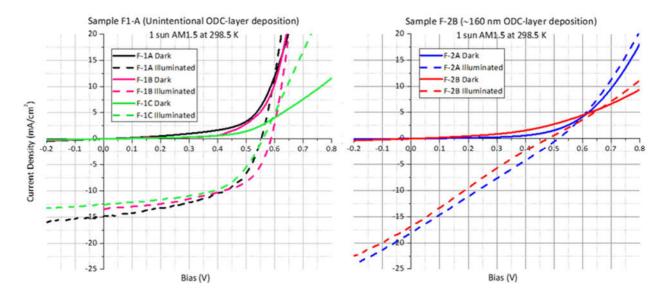

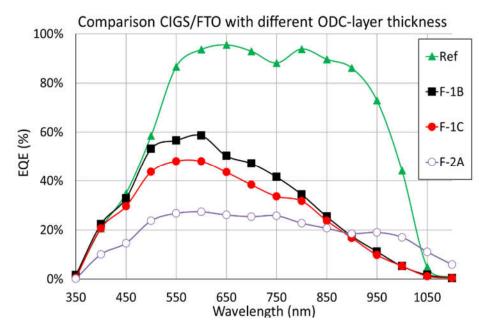

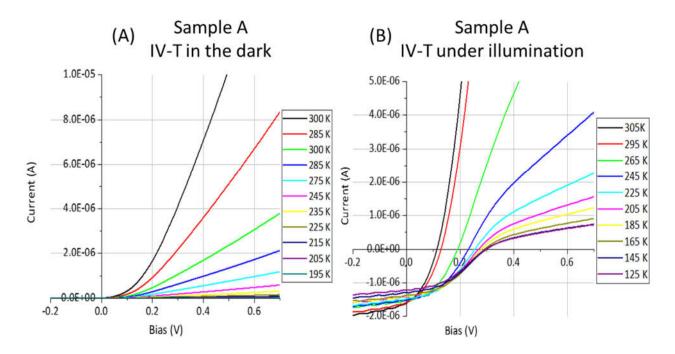

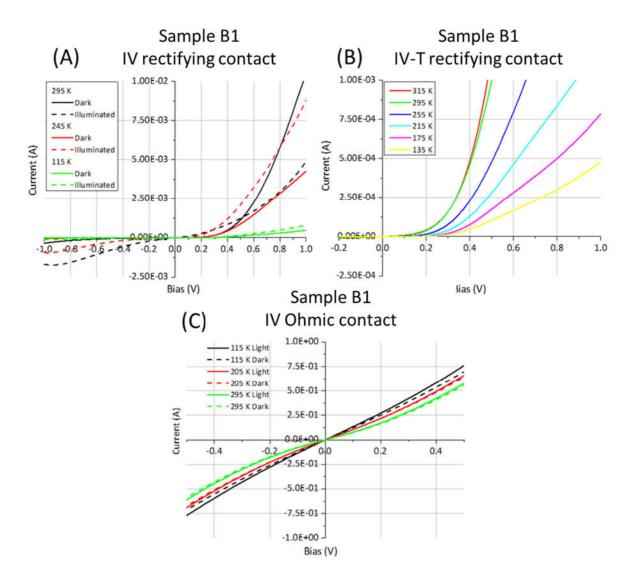

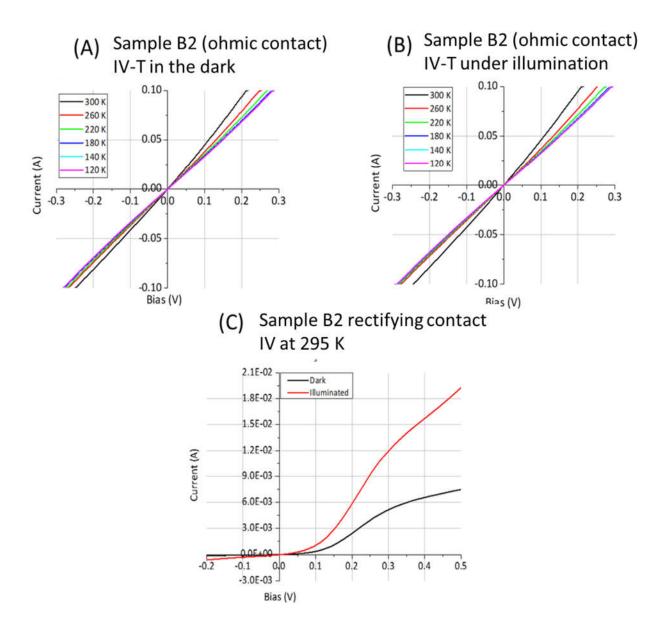

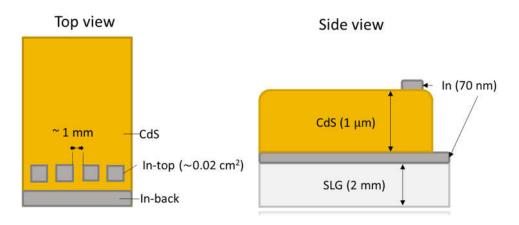

leads to only limited increase in  $V_{OC}$  and reduced device performance, most likely due to increased interface recombination (see section 2.3.1) [60] [61] [62].